### Lezioni di: Laboratorio di elettronica digitale

Anno Accademico 2006-2007

## **ELETTRONICA DIGITALE**

Laboratorio: lunedì 14:30-17:30

martedì 8:30-11:30

Lezioni: giovedì 14:30-17:30

## Corso di Laurea in Fisica e Astrofisica - a.a. 2006/07 SECONDO ANNO

| III TRIMESTRE                                                                            |         | Lunedì        |                                 | martedì         |                         | Mercole<br>dì  |             | giovedì          |                         | Venerdì |  |

|------------------------------------------------------------------------------------------|---------|---------------|---------------------------------|-----------------|-------------------------|----------------|-------------|------------------|-------------------------|---------|--|

|                                                                                          |         |               |                                 |                 |                         |                |             |                  |                         |         |  |

| ONDE ELETTR. E OTTICA (con meteorologia e sensoristica ambientale, II anno)              | Dalpiaz | 9.00-11.00    | Catt/1<br>9                     | 11.30-<br>13.30 | Catt/1<br>9             |                |             | 11.00 –<br>13.00 | Catt/1<br>9             |         |  |

|                                                                                          |         |               |                                 |                 |                         |                |             |                  |                         |         |  |

| LABORATORIO DI<br>ELETTRONICA<br>DIGITALE                                                | Savrié  | 14.30-17.30   | Lab.<br>elettr<br>onica<br>– F3 | 8.30-<br>11.30  | Lab.<br>elettr<br>onica |                |             | 14.30-<br>17.30  | Lab.<br>elettr<br>onica |         |  |

|                                                                                          |         |               |                                 |                 |                         |                |             |                  |                         |         |  |

| STUD.FUNZ.INT.FI<br>S.<br>(con meteorologia<br>e sensoristica<br>ambientale, II<br>anno) | Comelli | 11.00 – 13.00 | Catt/1<br>9                     |                 |                         | 8.30-<br>10.30 | Cat<br>t/19 | 9.00-<br>11.00   | Catt/1<br>9             |         |  |

A.A. 2006-07 3° trimestre

### occupazione laboratorio elettronica edificio F

| III TRIMESTRE                 | Lunedì      | martedì     | Mercoledì   | giovedì       | Venerdì      |

|-------------------------------|-------------|-------------|-------------|---------------|--------------|

| LABORATORIO DI<br>ELETTRONICA |             |             |             |               |              |

| Savrié                        | 14:30-17:30 | 11.30-13.30 |             | 14.30 – 17.30 |              |

| Marziani                      |             | 14.30-17.30 | 10.30-13.30 |               | 11.30– 13.30 |

| Andreotti                     |             |             | forse       |               | 8:30-11:30   |

### •ELETTRONICA

perché ci interessa?

### **SISTEMI TIPICI**

sistema informatico impianti HIFI

### **SEGNALI**

analogici digitali

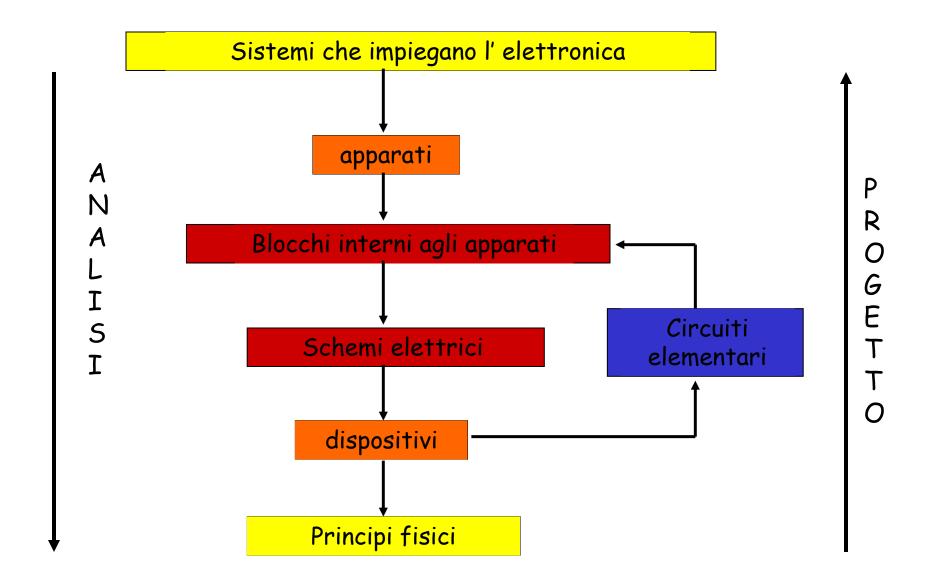

### •APPROCCIO SISTEMISTICO

sistemi

apparati

blocchi funzionali

schemi circuitali

componenti

→ sistema per la misura della velocità del suono

→ C.R.O.

→ amplificatore, trigger di Schmidt, alimentatori......

→ molto complessi

molto pochi e ricorrenti: circ. integrati e componenti

Riduce tutto, a qualunque livello, al concetto di blocco funzionale:

radio,TV, stereo, strumentazione varia.....

# Inserire un esempio di Circuito complesso

A.A. 2006-07 3° trimestre

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

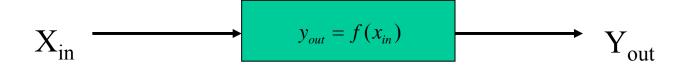

### IL BLOCCO FUNZIONALE

### Proprietà generali dei blocchi:

È completamente determinato dalla funzione che lega le variabili di ingresso e di uscita

### Possono essere:

Digitali : elettronica digitale

Analogici : elettronica analogica

Di conversione : A/D & D/A

### Possono anche essere:

Lineari e non lineari

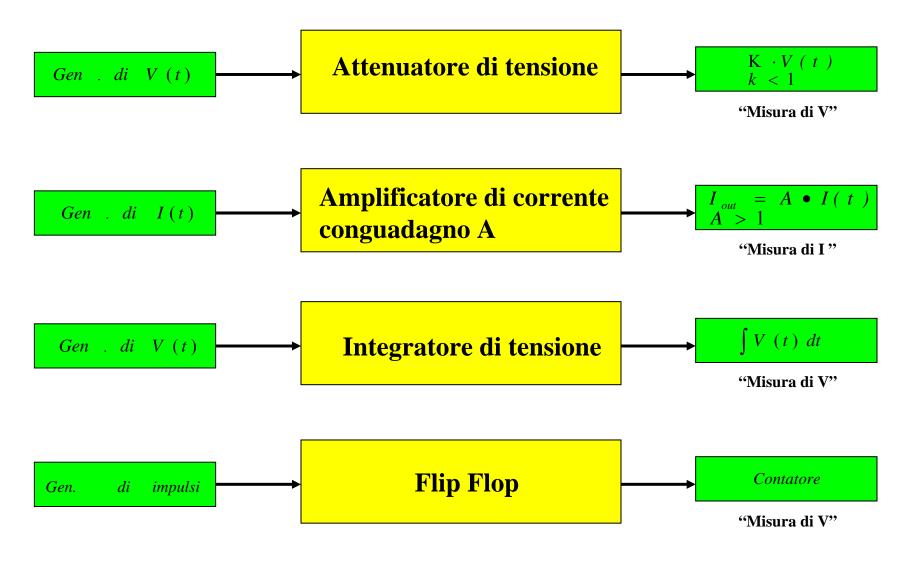

### **ESEMPI**

### PERCHE' APPROCCIO SISTEMISTICO?

- sistema = blocco

- blocco di natura elettronica

### PERCHE' PRIMA L'ELETTRONICA DIGITALE?

- più facile

- non richiede nozioni preliminari

- candidato ideale al tipo di approccio

- due soli stati (variaili di ingresso: tensioni)

fisici: H,L

logici: T,F; 1,0; ... sec. i gusti

•famiglie logiche:

TTL, HTL,ECL, MOS,CMOS....

• logica

positiva: H  $\longrightarrow$  T/1, L  $\longrightarrow$  F/0

negativa: L $\longrightarrow$ T/1, H $\longrightarrow$ F/0

•funzioni logiche

le stesse per tutte

| Family            | Basic<br>gate   | Fanout   | Pd<br>(mW/gate)                           | Noise<br>immunity | Prop. delay<br>(ns/gate) | Clock<br>(MHz) |

|-------------------|-----------------|----------|-------------------------------------------|-------------------|--------------------------|----------------|

| ${ m TTL}$        | NAND<br>NAND    | 10<br>10 | 10<br>22                                  | VG<br>VG          | 10<br>6                  | 35<br>50       |

| TTL-L             | NAND            | 20       | 1                                         | VG                | 33                       | 3              |

| TTL-LS            | NAND            | 20       | 2                                         | VG                | 9.5                      | 45             |

| TTL-S             | NAND            | 10       | 19                                        | VG                | 3                        | 125            |

| TTL-AS            | NAND            | 40       | 10                                        | VG                | 1.5                      | 175            |

| TTL-ALS           | NAND            | 20       | 1                                         | VG                | 4                        | 50             |

| ECL 10K           | OR-NOR          | 25       | 40-55                                     | P                 | 2                        | >60            |

| ECL100K           | OR-NOR          | ??       | 40-55                                     | P                 | 0.75                     | 600            |

| MOS               | NAND            | 20       | 0.2-10                                    | G                 | 300                      | 2              |

| 74C               | NOR/NAND        | 50       | 0.01/1                                    | VG                | 70                       | 10             |

| 74HC              | NOR/NAND        | 20       | 0.0025/0.6                                | VG                | 18                       | 60             |

| 74HCT             | NOR/NAND        | 20       | 0.0025/0.6                                | VG                | 18                       | 60             |

| 74AC              | NOR/NAND        | 50       | 0.005/0.75                                | VG                | 5.25                     | 100            |

| 74ACT             | NOR/NAND        | 50       | 0.005/0.75                                | VG                | 4.75                     | 100            |

| A.A. 2<br>3° trim | 006-07<br>estre |          | Prof. M.Savrié savr<br>http://www.fe.infn |                   |                          | 11             |

• la logica usata speculazione "intellettuale del XIX secolo:

### **ALGEBRA DI BOOLE**

- costanti: 0,1; T,F; H,L.....

- variabili: x,y,z.... ma ognuna ha 2 soli valori!

- funzioni: f(x,y,....) ...come sopra

- solo 3 operazioni (fondamentali):

NOT agisce solo su 1 var, cost. o funzione AND agisce su 2 o più var, cost. o funzioni OR agisce su 2 o più var, cost. o funzioni

### **POSTULATI....**

1)

$$A = 0$$

$o A = 1$

$$5) 0 + 0 = 0$$

$$2) 0 \bullet 0 = 0$$

$$6) 1 + 0 = 0 + 1 = 1$$

$$3)1 \bullet 1 = 1$$

$$7) 1 + 1 = 1$$

$$4)1 \bullet 0 = 0 \bullet 1 = 0$$

### ....& TEOREMI

1)

$$A + B = B + A$$

$A \bullet B = B \bullet A$

$$(2)(A + B) + C = A + (B + C)$$

$$(A \bullet B) \bullet C = A \bullet (B \bullet C)$$

$$3) A \bullet (B + C) = A \bullet B + A \bullet C$$

$$A + (B \bullet C) = (A + B) \bullet (A + C)$$

$$4) A + A = A \qquad A \bullet A = A$$

$$A \bullet A = A$$

$$5) \overline{\overline{A}} = A$$

6 )

$$A + (A \bullet B) = A$$

$A \bullet (A + B) = A$

7 )  $0 + A = 1 \bullet A = A$

$1 + A = 1 \quad 0 \bullet A = 0$

8 )  $A + A = 1 \quad A \bullet A = 0$

9 )  $A + A = 1 \quad A \bullet A = 0$

$A \bullet (A + B) = A \bullet B$

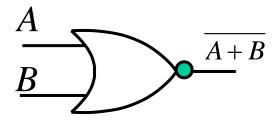

## Teorema di: DE MORGAN

### **FUNZIONI LOGICHE**

• si rappresentano con tabelle di verità

$$A + B = A + \overline{A}B$$

| A | В | A + B | $\overline{A}B$ | $A + \overline{A}B$ |

|---|---|-------|-----------------|---------------------|

| 0 | 0 | 0     | 0               | 0                   |

| 0 | 1 | 1     | 1               | 1                   |

| 1 | 0 | 1     | 0               | 1                   |

| 1 | 1 | 1     | 0               | 1                   |

$$A + (B \cdot C) = (A + B) \cdot (A + C)$$

| A                               | B                               | C                          | $B \cdot C$                     | $A+(B\cdot C)$                  | A+B                             | A + C                           | $(A+B)\cdot (A+C)$              |

|---------------------------------|---------------------------------|----------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|

| 0<br>0<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1 | 0<br>1<br>0<br>1<br>0<br>1 | 0<br>0<br>0<br>1<br>0<br>0<br>0 | 0<br>0<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>1<br>1<br>1 | 0<br>1<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>1<br>1<br>1<br>1 |

## Le funzioni logiche si possono: semplificare

### Definiamo:

| В | Α | minterm                           | maxterm                       |

|---|---|-----------------------------------|-------------------------------|

| 0 | 0 | $\overline{A} \cdot \overline{B}$ | A+B                           |

| 0 | 1 | $\overline{A} \cdot B$            | $A + \overline{B}$            |

| 1 | 0 | $A\cdot \overline{B}$             | $\overline{A} + B$            |

| 1 | 1 | $A \cdot B$                       | $\overline{A} + \overline{B}$ |

minterm=maxterm

maxterm=minterm

$$F\sum_{i=0}^{2^{n-1}}u_iP_i$$

## Esempi di semplificazione:

$$F_1 = \overline{a}b + a\overline{c} + \overline{a}c + a\overline{b} = \overline{a}b + a\overline{c} + \overline{b}c$$

$$F_{2} = \overline{a}\overline{b}c + \overline{a}b\overline{c} + \overline{a}bc + a\overline{b}c = \overline{a}\overline{c} + \overline{a}b + a\overline{b}c$$

$$F_{1} = \overline{a}b + a\overline{c} + \overline{a}\underline{c}(\underline{b} + \overline{b}) + a\overline{b}(\underline{c} + \overline{c}) =$$

$$\overline{a}b + a\overline{c} + \overline{a}cb + a\underline{c}b + a\overline{b}c + a\overline{b}c =$$

$$\overline{a}b(1+c) + a\overline{c}(1+\overline{b}) + \overline{b}c(a+\overline{a}) =$$

$$F_{2} = \overline{a}\overline{b}\overline{c} + \overline{a}b\overline{c} + \overline{a}bc + a\overline{b}c = \overline{a}\overline{c}(b+\overline{b}) + \overline{a}bc + a\overline{b}c = \overline{a}\overline{c}(1+b) + \overline{a}bc + a\overline{b}c = \overline{a}\overline{c} + \overline{a}\overline{c}b + \overline{a}bc + a\overline{b}c = \overline{a}\overline{c} + \overline{a}\overline{c}b + \overline{a}bc + a\overline{b}c = \overline{a}\overline{c}$$

A.A. 2006-07 3° trimestre

Prof. M.Savrié savrie@fe.infn.it $\overline{a}\overline{c} + \overline{a}b(c+\overline{c}) + a\overline{b}c$ http://www.fe.infn.it/~savrie/

# Le operazioni ed i simboli in elettronica (digitale)

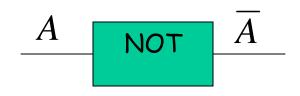

## 1) NOT

| A | X |

|---|---|

| L | Н |

| H | L |

A.A. 2006-07 3° trimestre

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

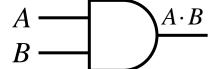

## 2) AND

| В | A | $A \cdot B$ |

|---|---|-------------|

| L | L | L           |

| L | H | L           |

| H | L | L           |

| H | H | Н           |

$$A \cdot B$$

$$A_i$$

$\prod_{i=1}^n A_i$

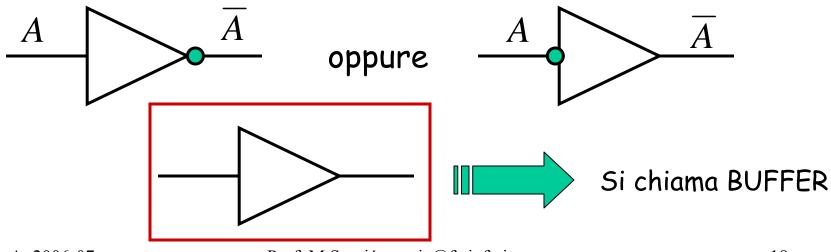

## 3) OR

| A |      |      |

|---|------|------|

|   | _) > | -A+B |

| R |      |      |

$$A_i$$

$\sum_{i=1}^n A_i$

| В | $\boldsymbol{A}$ | A + B |

|---|------------------|-------|

| L | L                | L     |

| L | Н                | Н     |

| H | L                | H     |

| H | Н                | Н     |

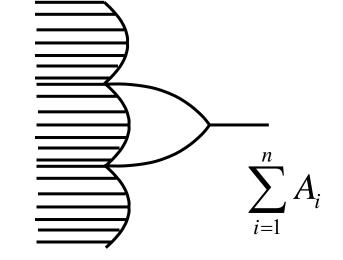

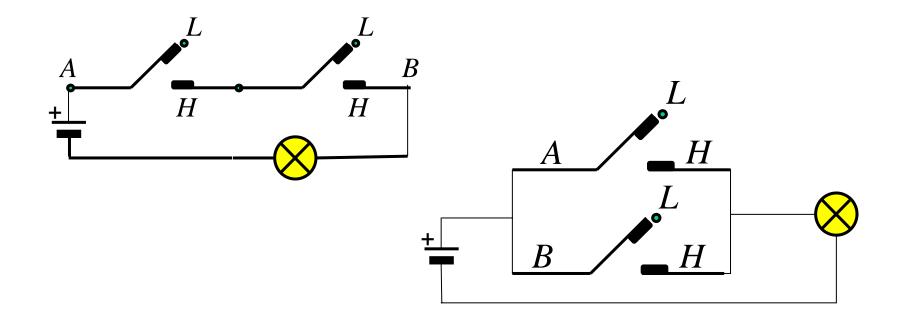

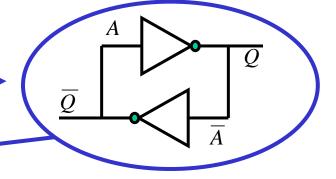

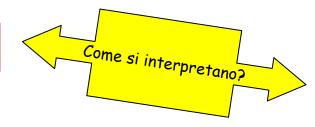

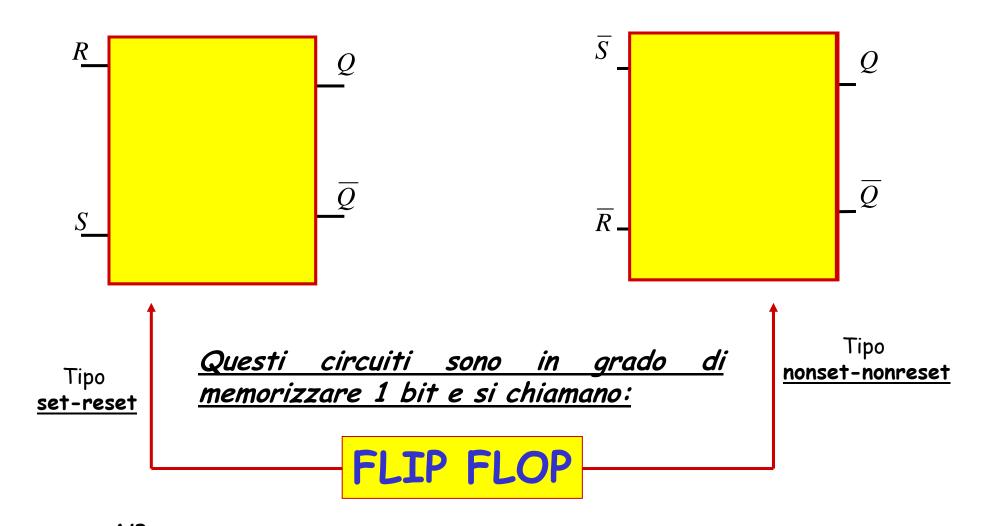

## Come li possiamo interfpretare?... la preistoria

L' interruttore è un dispositivo a due posizioni (L,H), una delle quali determina la chiusura del contatto elettrico fra i punti A e B mentre l'altra lascia sconnessi i due punti.

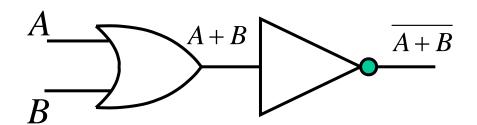

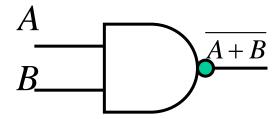

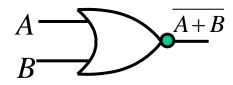

## 4) NOR

| A              | NOR   | A+B |

|----------------|-------|-----|

| $\overline{B}$ | 11011 |     |

| В | A | $\overline{A+B}$ |

|---|---|------------------|

| L | L | Н                |

| L | H | L                |

| H | L | L                |

| H | H | L                |

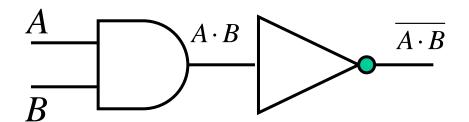

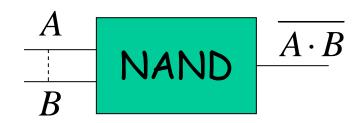

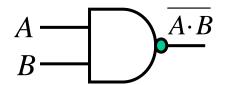

## 4) NAND

| В | $\boldsymbol{A}$ | $\overline{A\cdot B}$ |

|---|------------------|-----------------------|

| L | L                | Н                     |

| L | H                | H                     |

| H | L                | H                     |

| H | H                | L                     |

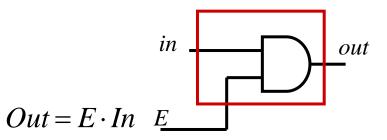

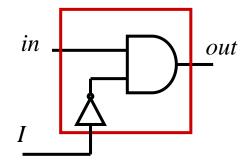

### ... Ma esistono altri circuiti "non fondamentali"

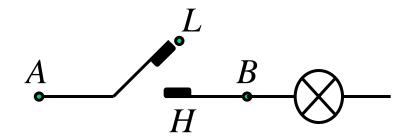

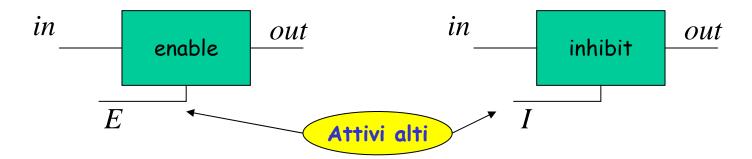

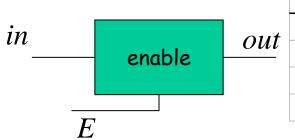

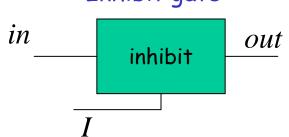

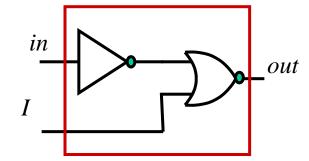

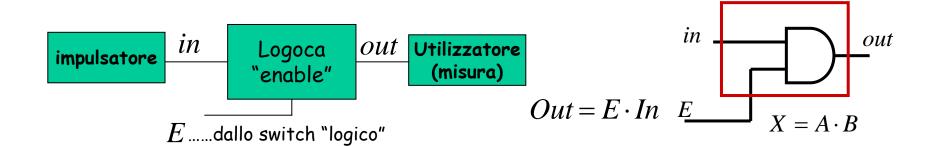

### Enable gate (strobe):

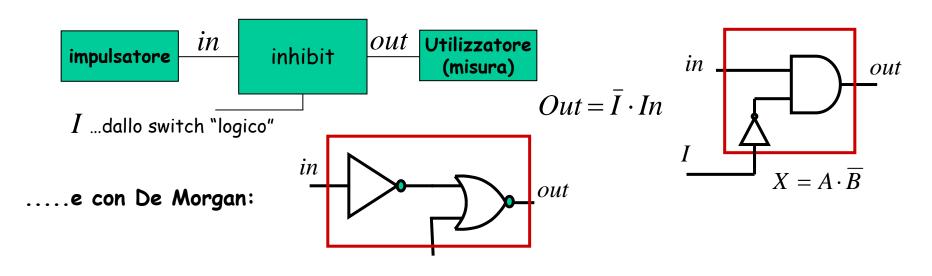

### Inhibit gate:

Un comando attivo svolge la funzione relativa al nome del blocco!!

### Enable gate (strobe):

| E | In | Out |

|---|----|-----|

| L | L  | L   |

| L | H  | L   |

| Н | L  | L   |

| Н | Н  | H   |

| _  |         |   |     |              |            |          |

|----|---------|---|-----|--------------|------------|----------|

| In | hıl     | n | + / | $\mathbf{n}$ | 11         | 0:       |

|    | , , , , |   | •   | y٠           | <b>4</b> 1 | <u> </u> |

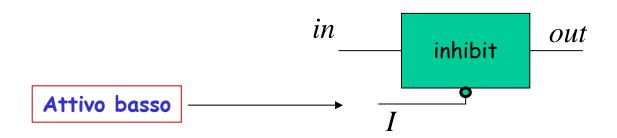

| I | In | Out |

|---|----|-----|

| L | L  | L   |

| L | H  | Н   |

| Н | L  | L   |

| Н | Н  | L   |

$$Out = \bar{I} \cdot In$$

....e con De Morgan:

A.A. 2006-07 3° trimestre

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

### Altre funzioni di due variabili:

| В | Α   | AB |  |

|---|-----|----|--|

| 0 | 0   | 0  |  |

| 0 | 1 0 |    |  |

| 1 | 0   | 0  |  |

| 1 | 1   | 1  |  |

| NOR |

|-----|

|-----|

| В | A | $\overline{A+B}$ |

|---|---|------------------|

| 0 | 0 | 1                |

| 0 | 1 | 0                |

| 1 | 0 | 0                |

| 1 | 1 | 0                |

**NAND**

| В | Α | $A \cdot B$ |

|---|---|-------------|

| 0 | 0 | 1           |

| 0 | 1 | 1           |

| 1 | 0 | 1           |

| 1 | 1 | 0           |

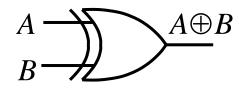

| В | Α | $A \oplus B$ |

|---|---|--------------|

| 0 | 0 | 0            |

| 0 | 1 | 1            |

| 1 | 0 | 1            |

| 1 | 1 | 0            |

OR

| В | A | A+B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

*EXNOR*

| В | Α | $\overline{A \oplus B}$ |  |

|---|---|-------------------------|--|

| 0 | 0 | 1                       |  |

| 0 | 1 | 0                       |  |

| 1 | 0 | 0                       |  |

| 1 | 1 | 1                       |  |

## Forma "normale" di una funzione "combinatoria"

### Somme di prodotti

$$\begin{split} \boldsymbol{X} &= \overline{A} \overline{B} \overline{C} \overline{D} + \overline{A} \overline{B} \underline{C} \underline{D} \\ &+ \overline{A} \underline{B} \overline{C} \overline{D} + A \overline{B} \overline{C} \overline{D} + \\ &+ A \overline{B} \overline{C} D + A \overline{B} C \overline{D} + A B C D \end{split}$$

$$\overline{X} = \overline{A}\overline{B}\overline{C}D + \overline{A}\overline{B}C\overline{D} + \overline{A}B\overline{C}D + \overline{A}B\overline{C}D + \overline{A}BCD + \overline{A}BCD + \overline{A}BCD + \overline{A}BCD + \overline{A}BCD + \overline{A}BCD$$

| Α | В | С | D | X | X | minterm                                 |

|---|---|---|---|---|---|-----------------------------------------|

| 0 | 0 | 0 | 0 | 1 | 0 | $\overline{ABCD}$                       |

| 0 | 0 | 0 | 1 | 0 | 1 | $\overline{A}\overline{B}\overline{C}D$ |

| 0 | 0 | 1 | 0 | 0 | 1 | $\overline{A}\overline{B}C\overline{D}$ |

| 0 | 0 | 1 | 1 | 1 | 0 | $\overline{A}\overline{B}CD$            |

| 0 | 1 | 0 | 0 | 1 | 0 | $\overline{A}B\overline{C}\overline{D}$ |

| 0 | 1 | 0 | 1 | 0 | 1 | $\overline{A}B\overline{C}D$            |

| 0 | 1 | 1 | 0 | 0 | 1 | $\overline{A}BC\overline{D}$            |

| 0 | 1 | 1 | 1 | 0 | 1 | $\overline{A}BCD$                       |

| 1 | 0 | 0 | 0 | 1 | 0 | $A\overline{B}\overline{C}\overline{D}$ |

| 1 | 0 | 0 | 1 | 1 | 0 | $A\overline{B}\overline{C}D$            |

| 1 | 0 | 1 | 0 | 1 | 0 | $A\overline{B}C\overline{D}$            |

| 1 | 0 | 1 | 1 | 0 | 1 | $A\overline{B}CD$                       |

| 1 | 1 | 0 | 0 | 0 | 1 | $AB\overline{CD}$                       |

| 1 | 1 | 0 | 1 | 0 | 1 | $AB\overline{C}D$                       |

| 1 | 1 | 1 | 0 | 0 | 1 | $ABC\overline{D}$                       |

| 1 | 1 | 1 | 1 | 1 | 0 | ABCD                                    |

$$X = (A + B + C + \overline{D}) \cdot (A + B + \overline{C} + D) \cdot (A + \overline{B} + C + \overline{D}) \cdot (A + \overline{B} + \overline{C} + \overline{D}) \cdot (A + \overline{D} + \overline{C} + \overline{D}) \cdot (A$$

Prodotti di Somme(si Prendono gli Zeri!!!!

A.A. 2006-07 3° trimestre

Prof. M.Savrié savrie@f http://www.fe.infn.it/~savrie/

Ottenuta come?

### Dimostriamo: Teorema di DE MORGAN (dalle tabelle di verità)

### Partiamo dalla AND:

| Α | В | X |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| $\overline{A}$ | $\overline{B}$ | $\overline{A \cdot B}$ |  |  |

|----------------|----------------|------------------------|--|--|

| 1              | 1              | 1                      |  |  |

| 1              | 0              | 1                      |  |  |

| 0              | 1              | 1                      |  |  |

| 0              | 0              | 0                      |  |  |

Cambiamo i nomi:

$$\overline{A} = C$$

$\overline{B} = D$   $\overline{X} = Y$

$$Y = C + D$$

$$\overline{\overline{A} \cdot \overline{B}} = A + B \qquad \overline{A} + B$$

$$\overline{\overline{A} + \overline{B}} = A \cdot B$$

### **N.B.**

Se uno schema logico (elettronico) realizza una certa funzione, per ottenerne il complemento basta scambiare le AND con le OR e complementare le variabili di ingresso

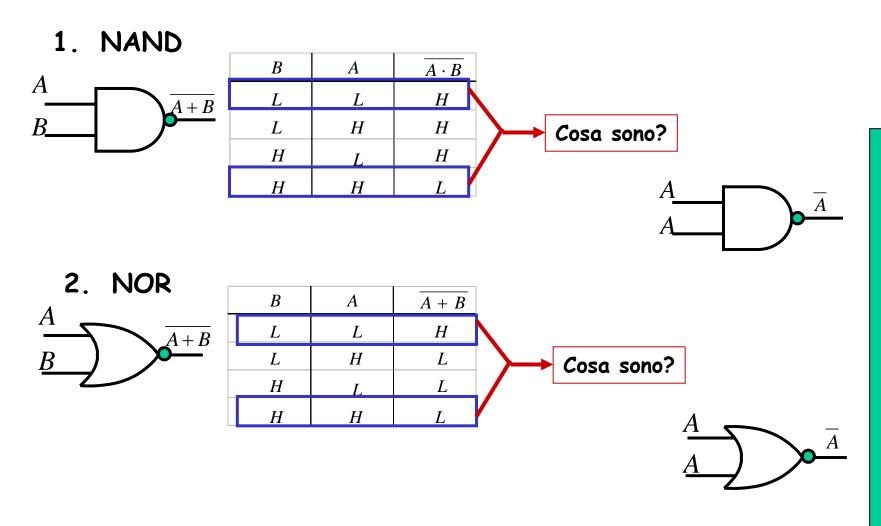

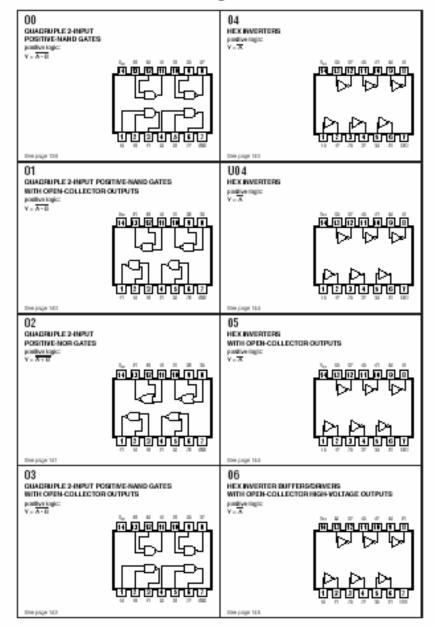

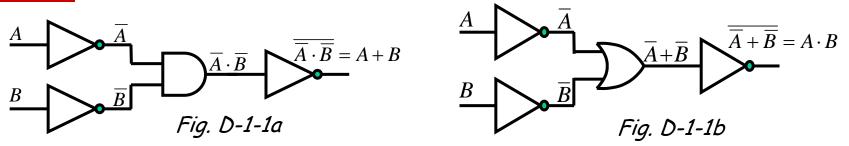

### Porte universali

### Dal teorema di De Morgan:

$$\overline{\overline{A} \cdot \overline{B}} = A + B$$

$\overline{\overline{A} + \overline{B}} = A \cdot B$

E' sufficiente realizzare il circuito corrispondente al primo membro e verificare che la sua tavola della verità sia uguale a quella del secondo membro.

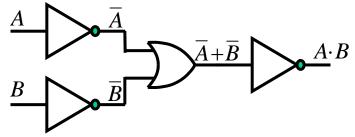

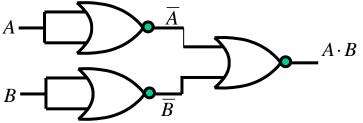

### Or con solo porte NAND

### AND con solo porte NOR

### Porte universali

### And con solo porte NAND

Or con solo porte NOR

$$\overline{\overline{A} \cdot B} = A \cdot B$$

$$A \longrightarrow \overline{A \cdot B}$$

$$\overline{\overline{A} + B} = A + B$$

$$A \longrightarrow \overline{A + B}$$

## Lezioni di: Laboratorio di elettronica digitale

Anno Accademico 2004-2005

Parte Seconda

## Esperienze di Laboratorio

## Scopo del Laboratorio di Elettronica Digitale

Circuiti: Analogici, Logici

sottosistemi a componenti: Discreti, Integrati

Realizzazioni di prototipi: uso delle breadboard

Circuiti Integrati: chip monolitici

Due grossi gruppi:

- gruppo bipolare: cariche positive e negative

- · gruppo unipolare: cariche di una sola polarità

I gruppi si diviodono in famiglie

Le famiglie sono caratterizzate da caratteristiche salienti All' interno delle famiglie i CI sono tutti compatibili tra loro

- ·Stessi livelli

- ·Stesse alimentazioni

- Potenze compatibili

Tra famiglie diverse i CI sono (in generale) incompatibili tra loro

### Circuiti di interfaccia

I principali parametri che caratterizzano le famiglie:

- 1. Ritardo di propagazione: maggiore nei circuiti unipolari

- 2. Dissipazione di potenza: inferiore negli unipolari

- 3. Capacità di pilotaggio (fan-out): maggiore negli unipolari

- 4. Immunità al rumore: migliore negli unipolari

- 5. Capacità di una porta (fan-in): equivalente

- 6. Densità di integrazione: maggiore ngli unipolari

La scelta va fatta in base alle caratteristiche/necessità di progetto

### Famiglie Bipolari:

- 1. RTL:obsoleta

- 2. DTL:obsoleta

- 3. HTL:

- 4. TTL standard:

- 5. TTL a bassa dissipazione:

- 6. TTL high speed:

- 7. TT Schottky:

- 8. ECL:

- 9. I<sup>2</sup>L:

### Famiglie unipolari:

- 1. P-MOS H.V.:

- 2. P-MO5 L.V.:

- 3. N-MOS:

- 4. *C*-MOS:

### Scale di Integrazione:

- 5(mall)5(cale)I(ntegration):

12 porte (50 transistor equivalenti)

- 2. M(edium)S(cale)I(tegration): 12-100 porte (50-500 trs equivalenti)

- 3. L(arge)S(cale)I(ntegration): 100-1000 porte (500-4000 trs equivalenti)

- V(ery)L(arge)S(cale)I(ntegration)

:

1000 porte (≥ 10<sup>7</sup> trs eq. per il

PENTIUM INTEL nel 2002)

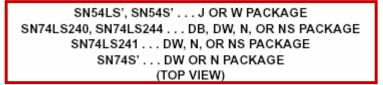

#### TI LOGIC DEVICE NOMENCLATURE

Are you confused by the device names and numbers of logic products? Do you need to know if a part has bus hold or series damping resistors? What kind of package the part is available in? The table below takes the mystery out of what all the letters and numbers in TI standard catalog logic devices represent. Take your favorite TI logic part number and find out what it can do.

| SN | 74 | LVC | Н | 16 | 2 | 244. | A   | $\mathbf{DGG}$ | R  |

|----|----|-----|---|----|---|------|-----|----------------|----|

| 11 | 2  | 3   | 4 | 5  | 6 | .7   | . 8 | 9:             | 10 |

#### 1. Standard Prefix

Example: SNJ - Conforms to MIL-PRF-38535 (QML)

#### 2. Temperature Range

- o 54 Military

- O 74 Comercial

#### 3. Family

#### 4. Special Features

- Blank = No Special Features

- C Configurable Vcc (LVCC)

- o D <u>Level-Shifting Diode</u> (CBTD)

- O H Bus Hold (ALVCH)

- o K Undershoot-Protection Circuitry (CBTK)

- R <u>Damping Resistor on Inputs/Outputs</u> (LVCR)

- S Schottky Clamping Diode (CBTS)

- o Z Power-Up 3-State (LVCZ)

#### Bit Width

- o Blank = Gates, MSI, and Octals

- o 1G Single Gate

- o 8 Octal IEEE 1149.1 (JTAG)

- o 16 Widebus™ (16, 18, and 20 bit)

- 18 Widebus IEEE 1149.1 (<u>JTAG</u>)

- 32 Widebus+™ (32 and 36 bit)

## A.A. 2006-07 3° trimestre

#### 6. Options

- o Blank = No Options

- 2 Series-Damping Resistor on Outputs

- o 4 Level Shifter

- o 25 25-ohm Line Driver

#### 7. Function

- O 244 Noninverting Buffer/Driver

- o 374 D-Type Flip-Flop

- 573 D-Type Transparent Latch

- o 640 Inverting Transceiver

#### 8. Device Revision

- o Blank = No Revision

- O Letter Designator A-Z

### 9. Packages

- D, DW Small-Outline Integrated Circuit (SOIC)

- DB, DL Shrink Small-Outline Package (SSOP)

- o DBB, DGV Thin Very Small-Outline Package (TVSOP)

- DBQ Quarter-Size Outline Package (QSOP)

- o DBV, DCK Small-Outline Transistor Package (SOT)

- o DGG, PW Thin Shrink Small-Outline Package (TSSOP)

- o FK Leadless Ceramic Chip Carrier (LCCC)

- o FN Plastic Leaded Chip Carrier (PLCC)

- o GB Ceramic Pin Grid Array (CPGA)

- O GKE, GKF MicroStar BGA™ Low-Profile Fine-Pitch Ball Grid Array (LFBGA)

- O GQL, GQN MicroStar Junior BGA Very-Thin-Profile Fine-

#### Pitch Ball Grid Array (VFBGA)

- O HFP, HS, HT, HV Ceramic Quad Flat Package (CQFP)

- J, JT Ceramic Dual-In-Line Package (CDIP)

- O N, NP, NT Plastic Dual-In-Line Package (PDIP)

- NS, PS Small Outline Package (SOP)

- PAG, PAH, PCA, PCB, PM, PN, PZ Thin Quad Flat Package (TQFP)

- PH, PQ, RC Quad Flat Package (QFP)

- W, WA, WD Ceramic Flat Package (CFP)

### 10. Tape and Reel

All new or changed devices in the **DB** and **PW** package types include the **R** designation for reeled product. Existing products designated as **LE** presently maintain that designation, but will be converted to **R** in the future.

#### Nomenclature Examples:

- For an Existing Device SN74LVTxxxDBLE

- O For a New or Changed Device SN74LVTxxxADBR

- O LE Left Embossed (valid for DB and PW packages only)

- R Standard (valid for all surface-mount packages except existing DB and PW devices)

#### **Family Comparison**

The table below compares some typical characteristics of several popular logic families available in the market today. The following sections provide brief explanations of the various parameters.

| Tunical                                  |                    |                    |                    |                    |                 | Logi           | c Fami             | lies             |                |                    |                    |                    |                    |

|------------------------------------------|--------------------|--------------------|--------------------|--------------------|-----------------|----------------|--------------------|------------------|----------------|--------------------|--------------------|--------------------|--------------------|

| Typical<br>Commercial                    |                    | П                  | TL                 |                    |                 | •              | CMOS               |                  |                |                    | E                  | CL                 |                    |

| Parameter<br>(0°C to +70°<br>C)          | LS                 | ALS                | АВТ                | FAST               | MG              | нс             | FACT               | LVC              | LCX            | 10H                | 100K               | ECL<br>in<br>PS(3) | E-<br>Lite         |

| Speed<br>Gate Prop<br>Delay (ns)         | 9                  | 7                  | 2.7                | 3                  | 65              | 8              | 5                  | 3.3              | 3.5            | 1                  | 0.75               | 0.33               | 0.22               |

| Flip-Flop<br>Toggle Rate<br>(MHz)        | 33                 | 45                 | 200                | 125                | 4               | 45             | 160                | 200              | 200            | 330                | 400                | 1,000              | 2800               |

| Output Edge<br>Rate (ns)                 | 6                  | 3                  | 3                  | 2                  | 50              | 4              | 2                  | 3.7              | 3.6            | 1                  | 0.7                | 0.5                | 0.25               |

| Power<br>Consumption<br>Per Gate<br>(mW) |                    |                    |                    |                    |                 |                |                    |                  |                |                    |                    |                    |                    |

| Quiescent                                | 5                  | 1.2                | 0.005              | 12,5               | 0.0006          | 0.003          | 0.0001             | 0.003            | 1E-<br>04      | 25                 | 50                 | 25                 | 73                 |

| Operating (1<br>MHz)                     | 5                  | 1.2                | 1.0                | 12.5               | 0.04            | 0.6            | 0.6                | 0.8              | 0.3            | 25                 | 50                 | 25                 | 73                 |

| Supply<br>Voltage (V)                    | +4.5<br>to<br>+5.5 | +4.5<br>to<br>+5.5 | +4,5<br>to<br>+5,5 | +4.5<br>to<br>+5.5 | +3<br>to<br>+18 | +2<br>to<br>+6 | +1.2<br>to<br>+3.6 | +2<br>to<br>+3.6 | +2<br>to<br>+6 | -4.5<br>to<br>-5.5 | -4.2<br>to<br>-4.8 | -4.2<br>to<br>-5.5 | -4.2<br>to<br>-5.5 |

| Output Drive<br>(mA)                     | 8                  | 8                  | 32/64              | 20                 | 1               | 4              | 24                 | 24               | 24             | 50<br>ohm<br>load  | 50<br>ohm<br>load  | 50<br>ohm<br>load  | 50<br>ohm<br>load  |

A.A. 2006-07

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

37

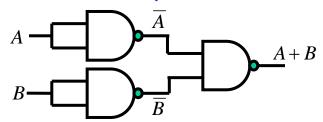

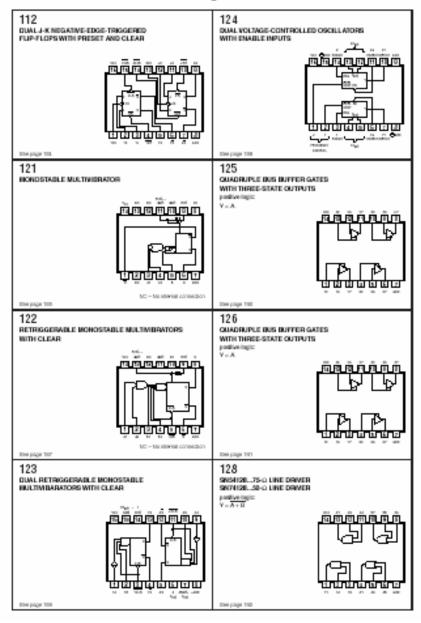

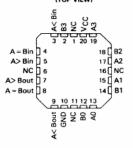

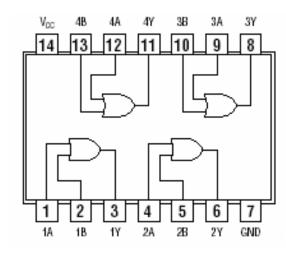

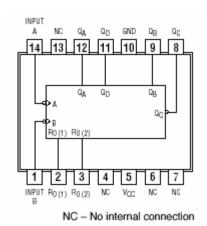

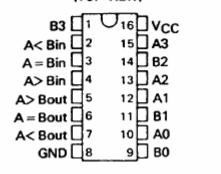

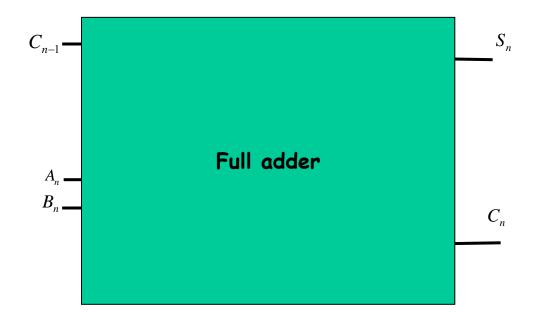

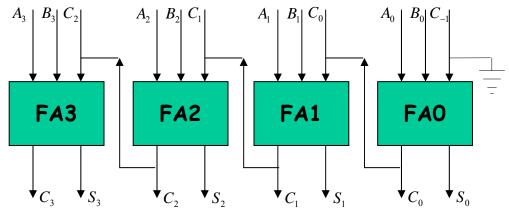

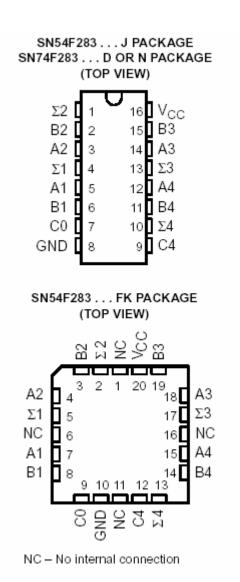

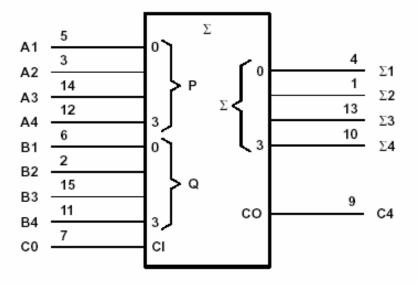

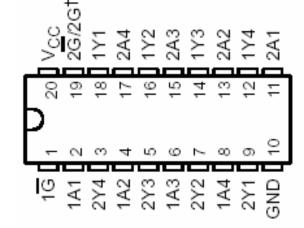

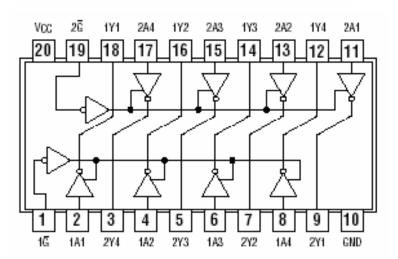

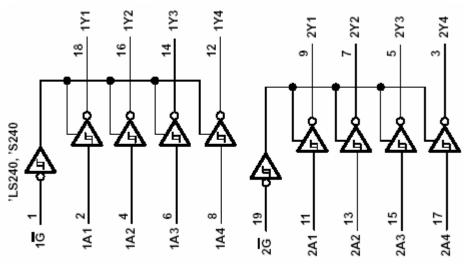

Pin Assignments

A.A. 2006-07 3° trimestre

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

A.A. 2006-07 3° trimestre

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

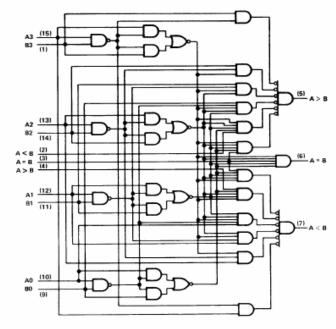

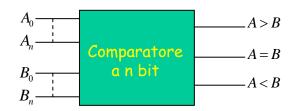

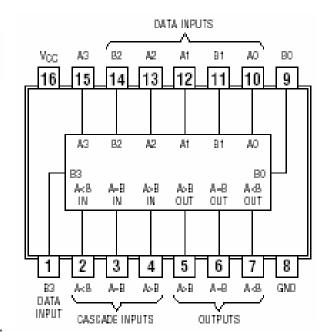

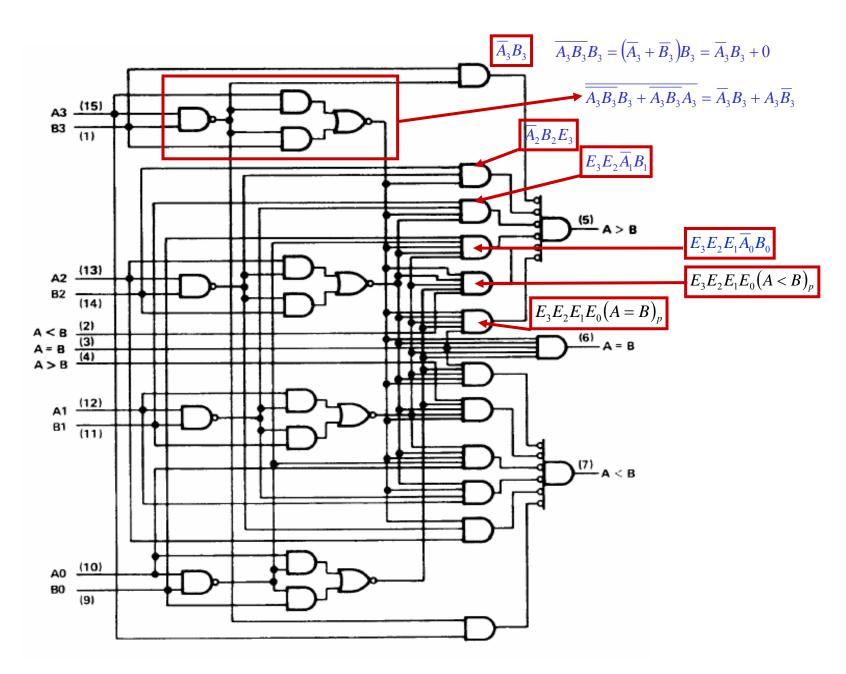

#### SN5485, SN54LS85, SN54S85 SN7485, SN74LS85, SN74S85 4-BIT MAGNITUDE COMPARATORS SDL5123 - MARCH 1974 - REVISED MARCH 1988

| TYPE          | TYPICAL<br>POWER | TYPICAL<br>DELAY |

|---------------|------------------|------------------|

|               | DISSIPATION      | (4-BIT WORDS)    |

| '85           | 275 mW           | 23 ns            |

| 1.585         | 52 mW            | 24 ns            |

| <b>'</b> \$85 | 365 mW           | 11 ns            |

#### description

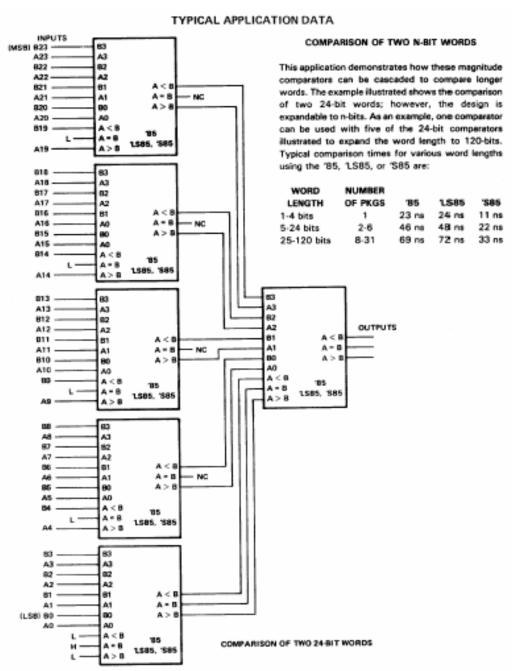

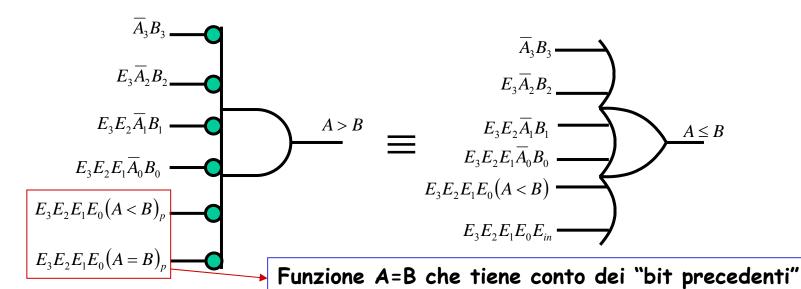

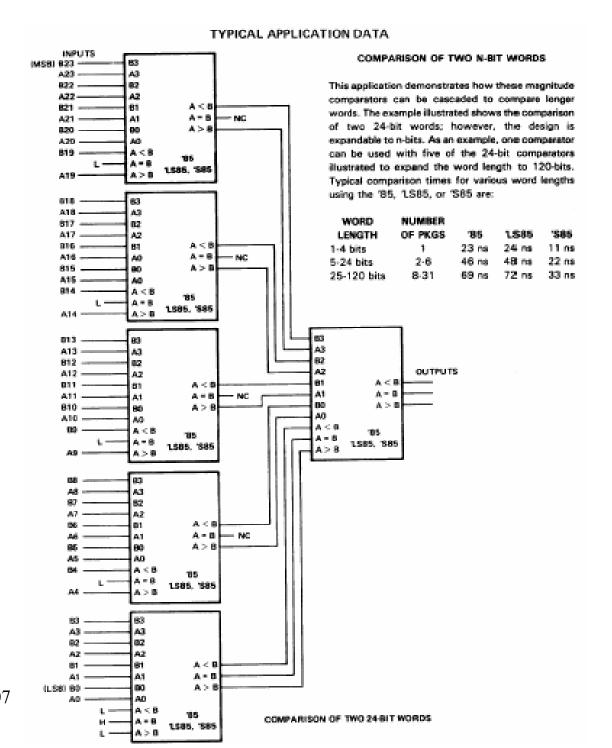

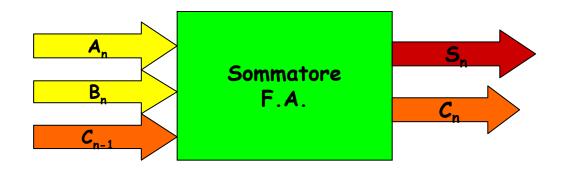

These four-bit magnitude comparators perform comparison of straight binary and straight BCD (8-4-2-1) codes. Three fully decoded decisions about two 4-bit words (A, B) are made and are externally available at three outputs. These devices are fully expandable to any number of bits without external gates. Words of greater length may be compared by connecting comparators in cascade. The A > B, A < B, and A = B outputs of a stage handling less-significant bits are connected to the corresponding A > B, A < B, and A = B inputs of the next stage handling more-significant bits. The stage handling the least-significant bits must have a high-level voltage applied to the A = B input. The cascading paths of the '85, 'LS85, and 'S85 are implemented with only a two-gate-level delay to reduce overall comparison times for long words. An alternate method of cascading which further reduces the comparison time is shown in the typical application data.

#### SN5485, SN54LS85, SN54S85 . . . J OR W PACKAGE SN7485 : . . N PACKAGE SN74LS85, SN74S85 . . . D OR N PACKAGE

#### SN54LS85, SN54S85 . . . FK PACKAGE (TOP VIEW)

NC - No internal connection

#### **FUNCTION TABLE**

|         |         | ARING<br>UTS |         |       | CASCADING<br>INPUTS |       | OUTPUTS |       |       |  |

|---------|---------|--------------|---------|-------|---------------------|-------|---------|-------|-------|--|

| A3, B3  | A2, B2  | A1, B1       | A0, B0  | A > B | A < B               | A = B | A > 8   | A < B | A = 8 |  |

| A3 > B3 | ×       | ×            | ×       | ×     | X                   | x     | н       | L     | L     |  |

| A3 < B3 | ×       | ×            | ×       | ×     | ×                   | х     | L       | н     | L     |  |

| A3 = B3 | A2 > B2 | ×            | ×       | x     | ×                   | x     | н       | L     | L     |  |

| A3 = B3 | A2 < B2 | ×            | ×       | x     | ×                   | x     | L       | н     | L     |  |

| A3 = B2 | A2 = B2 | A1 > B1      | ×       | ×     | ×                   | ×     | н       | L     | Ł     |  |

| A3 = B3 | A2 = B2 | A1 < B1      | ×       | x     | ×                   | x     | L       | н     | L     |  |

| A2 = B3 | A2 = B2 | A1 = B1      | A0 > B0 | ×     | ×                   | x     | н       | L     | L     |  |

| A3 = B3 | A2 = B2 | A1 = B1      | A0 < B0 | x     | ×                   | x     | L       | н     | L     |  |

| A3 = B3 | A2 = B2 | A1 = B1      | A0 = B0 | н     | L                   | L     | н       | L     | L     |  |

| A3 = B3 | A2 = B2 | A1 = B1      | A0 = B0 | L     | н                   | L     | L       | н     | L     |  |

| A3 = B3 | A2 = B2 | A1 - B1      | A0 = B0 | x     | x                   | н     | L       | L     | н     |  |

| A3 = B3 | A2 = B2 | A1 = B1      | A0 = B0 | н     | н                   | L     | L       | L     | L     |  |

| A3 = B3 | A2 = B2 | A1 = B1      | A0 = B0 | L     | L                   | L     | н       | Н     | L     |  |

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright @ 1988, Texas Instruments Incorporated

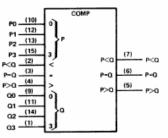

#### SN5485, SN54LS85, SN54S85 SN7485, SN74LS85, SN74S85 4-BIT MAGNITUDE COMPARATORS

logic diagrams (positive logic)

logic symbol<sup>†</sup>

<sup>†</sup>This symbol is in accordancee with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for D, J, N, and W packages.

2

A.A. 2006-07 3° trimestre

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

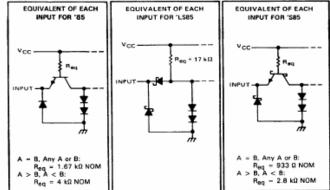

#### SN5485, SN54LS85, SN54S85 SN7485, SN74LS85, SN74S85 4-BIT MAGNITUDE COMPARATORS

SN5485, SN54LS85, SN54S85 SN7485, SN74LS85, SN74S85 4-BIT MAGNITUDE COMPARATORS

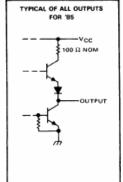

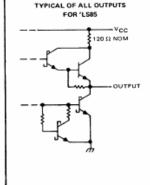

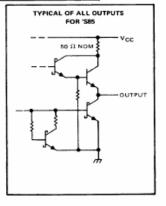

#### schematics of inputs and outputs

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

|                                              | SN54'<br>SN545' | SN54LS* | SN74'<br>SN74S' | SN74LS | UNIT |

|----------------------------------------------|-----------------|---------|-----------------|--------|------|

| Supply voltage, V <sub>CC</sub> (see Note 1) | 7               | 7       | 7               | 7      | V    |

| Input voltage                                | 5.5             | 7       | 5.5             | 7      | v    |

| Interemitter voltage (see Note 2)            | 5.5             |         | 5.5             |        | V    |

| Operating free-air temperature range         | - 66            | to 125  | -0              | to 70  | °C   |

| Storage temperature range                    | -65             | to 150  | - 65            | to 150 | °C   |

NOTES: 1. Voltage values, except interemitter voltage, are with respect to network ground terminal.

This is the voltage between two emitters of a multiple-emitter input transistor. This rating applies to each A input in conjunction with its respective 8 input of the "85 and "S85.

#### recommended operating conditions

|                                    |     | SN5485 |      |      | SN7485 |      |      |  |

|------------------------------------|-----|--------|------|------|--------|------|------|--|

|                                    | MIN | NOM    | MAX  | MIN  | NOM    | MAX  | UNIT |  |

| Supply voltage, V <sub>CC</sub>    | 4.5 | 5      | 5.5  | 4.75 | 5      | 5.25 | ٧    |  |

| High-level output current, IOH     |     |        | -400 |      |        | -400 | μA   |  |

| Low-level output current, IOL      |     |        | 16   |      |        | 16   | mA   |  |

| Operating free-air temperature, TA | -55 |        | 125  | 0    |        | 70   | ,c   |  |

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|       | PARAMETER                      |                                         | TE                                                 | ST CONDITI | IONS†                |                       | MIN | TYPI | MAX          | UNI |

|-------|--------------------------------|-----------------------------------------|----------------------------------------------------|------------|----------------------|-----------------------|-----|------|--------------|-----|

| VIH   | High-level input voltage       |                                         |                                                    |            |                      |                       | 2   |      |              | V   |

| VII.  | Low-level input voltage        |                                         |                                                    |            |                      |                       |     |      | 0.8          | v   |

| VIK   | Input clamp voltage            |                                         | VCC - MIN,                                         |            | $t_{\parallel} = -1$ | 12 mA                 |     |      | -1.5         | v   |

| Vон   | High-level output voltage      |                                         | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0,8 V, |            | VIH =                | 2 V,<br><b>400</b> μΑ | 2.4 | 3,4  |              | ٧   |

| VOL   | Low-level output voltage       |                                         | V <sub>CC</sub> = MIN.<br>V <sub>IL</sub> = 0.8 V, |            | VIH -                | 2 V.<br>16 mA         |     | 0,2  | 0.4          | ٧   |

| 4     | Input current at maximum inp   | sut voltage                             | VCC = MAX,                                         |            | V <sub>1</sub> = 5   | .5 V                  |     |      | 1            | m/  |

| ΉΗ    | High-level input current       | A < B, A > B inputs<br>all other inputs | V <sub>CC</sub> = MAX.                             |            | V <sub>1</sub> = 2   | .4 V                  | -   |      | 120          | μА  |

| 'IL   | Low-level input current        | A < B, A > B inputs<br>all other inputs | VCC = MAX.                                         |            | v <sub>1</sub> = 0   | ,4 V                  |     |      | -1.6<br>-4.8 | mi  |

| los   | Short-circuit output current 9 |                                         | V <sub>CC</sub> = MAX.                             | Vo = 0     |                      | SN5485                | -20 |      | -55          |     |

|       |                                |                                         |                                                    |            |                      | SN7485                | -18 |      | -55          | _   |

| lcc - | Supply current                 |                                         | VCC = MAX.                                         | See Note 4 |                      |                       | 1   | 55   | 88           | m/  |

<sup>\*</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

#### switching characteristics, VCC = 5 V, TA = 25°C

| PARAMETER <sup>1</sup> | FROM                   | TO           | NUMBER OF<br>GATE LEVELS | TEST CONDITIONS | MIN TYP | MAX | UNIT |

|------------------------|------------------------|--------------|--------------------------|-----------------|---------|-----|------|

|                        |                        |              | 1                        |                 | 7       |     |      |

|                        |                        | A < B, A > B | 2                        | 1               | 12      |     |      |

| <sup>†</sup> PLH       | Any A or B data input  |              | 3                        | 1               | 17      | 26  | m.   |

|                        |                        | A = 8        | 4                        | 1               | 23      | 35  |      |

|                        | 1                      | 11           |                          |                 |         |     |      |

|                        |                        | A < B, A > B | 2                        | CL = 15 pF,     | 15      |     | l    |

| 1PH L                  | Any A or II data input |              | 3                        |                 | 20      | 30  | ns   |

|                        | A = B 4 See Note 5     |              |                          |                 | 20      | 30  |      |

| ₩LH                    | A. < 8 or A = 8        | A > B        | 1                        | 300 14010 0     | 7       | 11  | ns   |

| 1PHL                   | A. < B or A = B        | A > B        | 1                        | 1               | 11      | 17  | ns   |

| <sup>1</sup> PLH       | A = 8                  | A - B        | 2                        | 1               | 13      | 20  | 795  |

| THIL.                  | A = B                  | A = 8        | 2                        | 1               | 11      | 17  | ms   |

| <sup>1</sup> PLH       | A. > B or A = B        | A < B        | 1                        | 1               | 7       | 11  | ns   |

| TPHL                   | A. > 8 or A = 8        | A < B        | 1                        | 1               | 11      | 17  | ns   |

<sup>\$</sup>tp[H = propagation delay time, low-to-high-level output

FAIL typical values are at VCC = 5 V, TA = 25°C.

Not more than one output should be shorted at a time.

NOTE 4: I CC is measured with outputs open, A = R grounded, and all other inputs at 4.5 V.

tpHL = propagation dalay time, high-to-low-level output

NOTE 5: Load circuits and voltage waveforms are shown in Section 1.

### SN5485, SN54LS85, SN54S85 SN7485, SN74LS85, SN74S85 4-BIT MAGNITUDE COMPARATORS SDL5125-MARCH 1974-PREVISED MARCH 1988

#### SN5485, SN54LS85, SN54S85 SN7485, SN74LS85, SN74S85 4-BIT MAGNITUDE COMPARATORS

#### recommended operating conditions

|                                    | SN54LS85 |     |      | SN74LS85 |     |      | LINIT |

|------------------------------------|----------|-----|------|----------|-----|------|-------|

|                                    | MIN      | NOM | MAX  | MIN      | NOM | MAX  | CONT  |

| Supply voltage, V <sub>CC</sub>    | 4.5      | 5   | 5.5  | 4.75     | 5   | 5.25 | ٧     |

| High-level output current, IOH     |          |     | -400 |          |     | -400 | μA    |

| Low-level output current, IOL      |          |     | 4    |          |     | 8    | mA    |

| Operating free-air temperature, TA | ~55      |     | 125  | 0        |     | 70   | ,c    |

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|      |                             |                     |                                                                  |                                                                 | - 5           | N54L88 | 16   | S   | N74LS8 | 15   | UNIT  |

|------|-----------------------------|---------------------|------------------------------------------------------------------|-----------------------------------------------------------------|---------------|--------|------|-----|--------|------|-------|

|      | PARA                        | METER               | TEST COM                                                         | IDITIONST                                                       | MIN           | TYP!   | MAX  | MIN | TYP‡   | MAX  | UNIT  |

| VIII | High-level input            | voltage             |                                                                  |                                                                 | 2             |        |      | 2   |        |      | ٧     |

| VIL  | Low-level input             |                     |                                                                  |                                                                 |               |        | 0.7  |     |        | 0.7  | ٧     |

| VIK  | Input clamp vol             | tage                | V <sub>CC</sub> = MIN,                                           | I <sub>I</sub> = -18 mA                                         |               |        | -1.5 |     |        | -1.5 | ٧     |

|      | High-level outp             | ut voltage          | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = V <sub>IL</sub> max, | V <sub>IH</sub> = 2 V,<br>I <sub>OH</sub> = -400 <sub>A</sub> A | 2.5           | 3.4    |      | 2.7 | 3.4    |      | v     |

|      |                             |                     | V <sub>CC</sub> = MIN,                                           | IOL = 4 mA                                                      |               | 0.25   | 0.4  |     | 0.25   | 0.4  | v     |

| VOL  | Low-level output voltage    |                     | V <sub>IH</sub> = 2 V,<br>V <sub>IL</sub> = V <sub>IL</sub> max  | 1 <sub>DL</sub> = 8 mA                                          |               |        |      |     | 0.35   | 0.5  | Ľ     |

|      | Input ourrest               | A < B, A > B inputs |                                                                  |                                                                 |               |        | 0.1  |     |        | 0.1  | Γ.    |

| 4    | at maximum<br>input voltage | all other inputs    | V <sub>CC</sub> = MAX;                                           | V <sub>1</sub> - 7 V                                            |               |        | 0.3  |     |        | 0.3  | mA    |

|      | High-level                  | A < B, A > B inputs |                                                                  | W27-4                                                           | $\overline{}$ |        | 20   |     |        | 20   | uA.   |

| чн   | input current               | all other inputs    | VCC - MAX.                                                       | V <sub>1</sub> = 2.7 V                                          |               |        | 60   |     |        | 60   | 1"    |

|      | Low-level                   | A < 8, A > 8 inputs | V MAY                                                            | W Date                                                          |               |        | -2.4 |     |        | -0.4 | mA.   |

| HL.  | input current               | all other inputs    | VCC = MAX.                                                       | V1 - 0.4 V                                                      |               |        | -1.2 |     |        | -1.2 |       |

| los  | Short-circuit ou            | rtput current §     | VCC = MAX                                                        |                                                                 | -20           |        | -100 | 20  |        | -100 | mA    |

| loc. | Supply current              |                     | VCC = MAX,                                                       | See Note 4                                                      |               | 10.4   | 20   |     | 10.4   | 20   | ∫ maA |

<sup>1</sup> For conditions shown as MIN or MAX, use the appropriate value specifies under recommended operating conditions.

NOTE 4:  $I_{CC}$  is measured with outputs open, A = 8 grounded, and all other inputs at 4.5 V.

#### switching characteristics, VCC = 5 V, TA = 25°C

| PARAMETER <sup>1</sup> | FROM                  | TO<br>OUTPUT | NUMBER OF<br>GATE LEVELS  | TEST CONDITIONS                      | MIN | TYP | MAX | UNIT  |

|------------------------|-----------------------|--------------|---------------------------|--------------------------------------|-----|-----|-----|-------|

|                        |                       |              | - 1                       |                                      |     | 14  |     | 1     |

|                        |                       | A<0,A>0      | 2                         |                                      |     | 19  |     |       |

| 1PLH                   | Any A or B data input |              | 3                         | 1                                    |     | 24  | 36  | ] ''' |

|                        |                       | A = B        | 4                         | 1                                    |     | 27  | 45  | 1     |

|                        |                       |              | 1                         | 1                                    |     | 11  |     |       |

|                        |                       | A < B, A > 8 | 2                         |                                      |     | 15  |     | ۰.,   |

| PHL                    | Any A or 8 data input |              | 3 C <sub>L</sub> = 15 pF. |                                      | 20  | 30  | 1 " |       |

|                        |                       | A = 8        | 4                         | R <sub>L</sub> = 2 kΩ,<br>See Note 5 |     | 23  | 45  | 1_    |

| PLH                    | A < B or A = B        | A > 8        | 1                         |                                      |     | 14  | 22  | ns    |

| THIL.                  | A < 8 or A = 8        | A > 0        | 1                         | 1                                    |     | 11  | 17  | m     |

| 1PLH                   | A = B                 | A - B        | 2                         | 1                                    |     | 13  | 20  | ns    |

|                        |                       | A = B        | 2                         | 1                                    |     | 13  | 76  | m     |

|                        | A > 8 or A = 8        | A < 8        | 1                         | ſ                                    |     | 14  | 22  | m     |

|                        | A > 8 or A = 8        | A < 9        | 1                         | 1                                    |     | 11  | 17  | 711   |

TopLH = propagation delay time, low-to-high-level output trel. = propagation delay time, high-to-low-level output

NOTE 5: Load circuits and voltage waveforms are shown in Section 1.

#### recommended operating conditions

|                                    |     | SN54585 |     |      | SN74585 |      |      |

|------------------------------------|-----|---------|-----|------|---------|------|------|

|                                    | MIN | NON     | MAX | MIN  | NOM     | MAX  | UNIT |

| Supply voltage, V <sub>CC</sub>    | 4.5 | 5       | 5.5 | 4.75 | 5       | 5.25 | v    |

| High-level output current, IOH     |     |         | -1  |      |         | -1   | mA   |

| Low-level Output current, IQL      |     | _       | 20  |      |         | 20   | mA   |

| Operating tree-air temperature, TA | -55 |         | 125 | 0    |         | 70   | "C   |

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|      | PARAMETE                     | :R                  | TES                                  | T CONGITIONS              | ;†       | 64788 | TYP: | MAX  | UNIT |

|------|------------------------------|---------------------|--------------------------------------|---------------------------|----------|-------|------|------|------|

| VIII | High-level input voltage     |                     |                                      |                           |          | 2     |      |      | v    |

| VIL  | Low-level input voltage      |                     |                                      |                           |          |       |      | 0.8  | v    |

| VIIK | Input clamp voltage          |                     | V <sub>CC</sub> = MIN,               | I <sub>1</sub> = -18 mA   |          | -     |      | -1.2 | v    |

|      |                              |                     | VCC - MIN,                           | V <sub>IM</sub> = 2 V.    | SN54S85  | 2.5   | 3.4  |      | l v  |

| VOH  | High-level output voltage    |                     | VIL - 0.8 V.                         | I <sub>OH</sub> = -1 mA   | SN74S85  | 2.7   | 3.4  |      |      |

|      |                              |                     | Vcc - MIN.                           | V <sub>IH</sub> = 2 V,    | -        |       |      | 0.5  | v    |

| VOL  | Low-level output voltage     |                     | VIL = 0.8 V,                         | OL = 20 mA                |          |       |      | 0.5  | ٠.   |

| 4    | Input current at maximum ing | ut voltage          | VCC - MAX.                           | V, - 55 V                 |          |       |      | 1    | mA   |

|      |                              | A < 8, A > B inputs | Ween lank                            |                           |          |       |      | 50   | aA.  |

| 4111 | High-level input current     | all other inputs    | Voc - MAX,                           | V <sub>1</sub> = 2.7 V    |          |       |      | 150  | , an |

|      |                              | A < B, A > B inputs |                                      |                           |          |       |      | -2   | mA   |

| HL.  | Low-level input current      | all other inputs    | V <sub>CC</sub> = MAX,               | V1 - 0.5 V                |          |       |      | -6   | ma.  |

| los  | Short-circuit output current |                     | V <sub>DC</sub> - MAX                |                           |          | -40   |      | -100 | mA.  |

| - Gu |                              |                     | V <sub>CC</sub> - MAX,               | See Note 4                |          |       | 73   | 115  |      |

| 1CC  | Supply current               |                     | V <sub>CC</sub> = MAX,<br>See Note 4 | T <sub>.</sub> A = 125°C, | SN54585W |       |      | 110  | mA.  |

For conditions shown as MIN or MAX, use the eppropriate Value specified under recommended operating conditions.

All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

Not more than one output should be shorted at a time, and journation of the short-circuit should not exceed one tecond

NOTE 4: foc is measured with outputs open, A = 6 groundly, and all other inputs at 4.5 V.

#### switching characteristics, VCC = 5 V, TA = 25°C

| PARAMETER <sup>1</sup> | FROM                  | TO                               | NUMBER OF<br>GATE LEVELS | TEST CONDYTIONS                                      | MIN TYP | MAX  | UNI |  |

|------------------------|-----------------------|----------------------------------|--------------------------|------------------------------------------------------|---------|------|-----|--|

|                        |                       |                                  | 1                        |                                                      | 5       | 5    |     |  |

|                        |                       | A < B, A > B                     | 2                        |                                                      | 7.5     |      |     |  |

| *PLH                   | Any A or B data input |                                  | 3                        |                                                      | 10.5    | 16   | ~   |  |

|                        |                       | A - B                            | 4                        | 1                                                    | 12      | _18  |     |  |

|                        | Any A or B data input | y A or B data inpuj A < B, A > B | 1                        | C <sub>L</sub> = 15 pF,<br>PL = 280 fL<br>See Note 5 | 5.5     |      |     |  |

|                        |                       |                                  | 2                        |                                                      | 7       | -    |     |  |

| tPHL.                  |                       |                                  | 3                        |                                                      | 11      | 16.5 |     |  |

|                        |                       | A = 8                            | 4                        |                                                      | 11      | 16.5 |     |  |

| 1PLH                   | A < B or A = B        | A > B                            | 1                        |                                                      |         | 7.5  | ma  |  |

| TPHL                   | A < B or A = B        | A > 0                            | 1                        |                                                      | _ 5.5   | 8.5  | 06  |  |

| <sup>1</sup> PLH       | A - B                 | A = 8                            | 2                        |                                                      | 7       | 10.5 | 76  |  |

| 1PHL                   | A = 9                 | A = B                            | 2                        |                                                      | 5       | 7.5  | ns  |  |

| 1PLH                   | A > 8 to A = 8        | A < 8                            | 1                        | 1                                                    | 5       | 7.5  | ns. |  |

| <sup>1</sup> PHIL      | A > 5 or A = B        | A < 8                            | 1                        | 1                                                    | 5.5     | 8.5  | ns  |  |

<sup>1</sup>cpLH = propagation delay time, low-to-high-level output

topp, - propagation defer sime, high-to-low-level output NOTE 5: Load circuits and voltage exeveforms are shown in Section 1.

TAII typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

What more than one output should be shorted at a time, and duration of the short-circuit should not exceed one second

A.A. 2006-07 3° trimestre

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

## Noi useremo, in generale, integrati (C.I.) della famiglia TTL (STANDARD?)

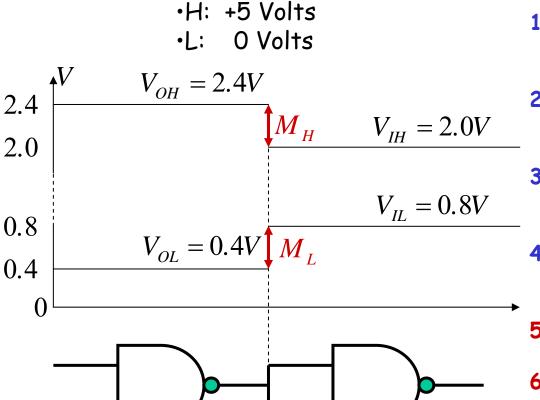

## Livelli di ingresso/uscita:

- 1. V<sub>OH</sub>=minimo valore dello stato alto garantito in uscita

- V<sub>OL</sub>=massimo valore dello stato basso garantito in uscita

- V<sub>IH</sub>=minimo valore dello stato alto richiesto in ingresso

- V<sub>IL</sub>=massimo valore dello stato basso richiesto in ingresso

- M<sub>H</sub>=margine di rumore nello stato basso

- M<sub>L</sub>=margine di rumore nello stato alto

A.A. 2006-07 3° trimestre

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

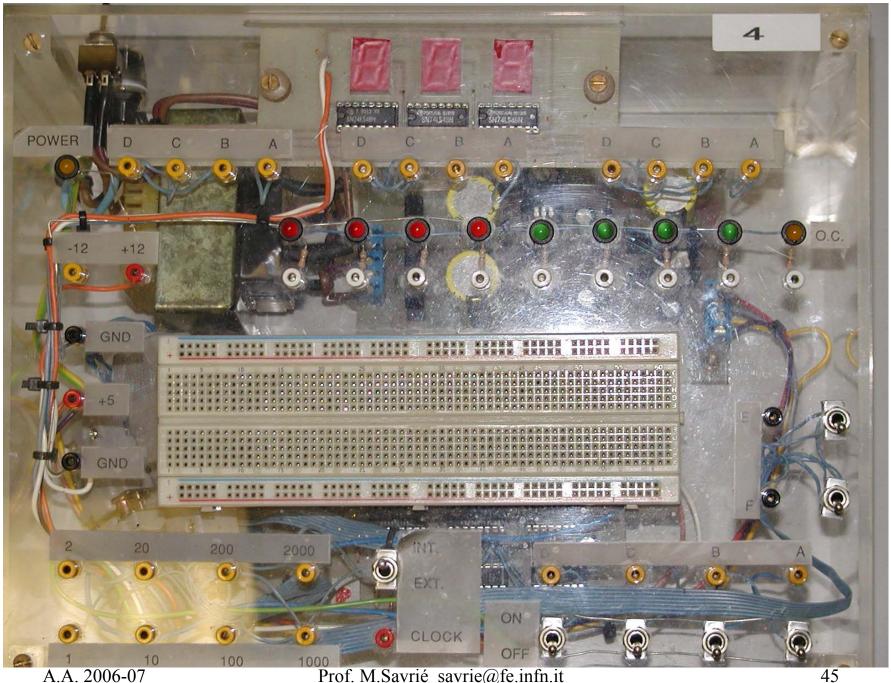

# Uso del "laboratorio logico"

- 1.  $V_A$ = tensione riferita a massa

- 2.  $V_B-V_A$ =tensione "fuori massa"

Le basette ("laboratorio logico") sono dotate di:

- Breadboard

- ·Alimentazioni: +5V,+12V,-12V

- •Clock:1KHz,(2KHz),10KHz,(20KHz),100KHz,(200KHz), 1000KHz,(2000KHz)

- Commutatori (switch)

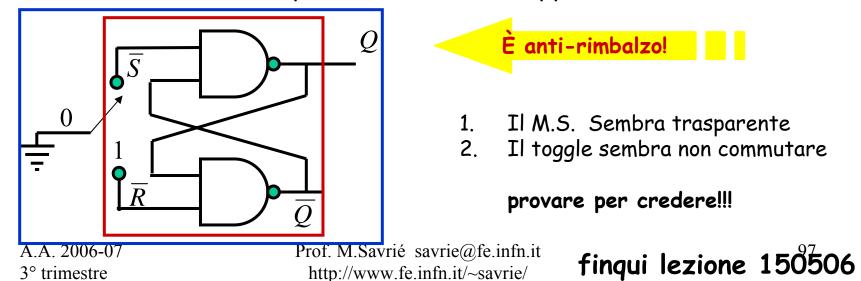

- ·Commutatori anti-rimbalzo

- ·Led (active high)

- ·Led o.c. (active low)

- Display a 7 segmenti

## Importante:

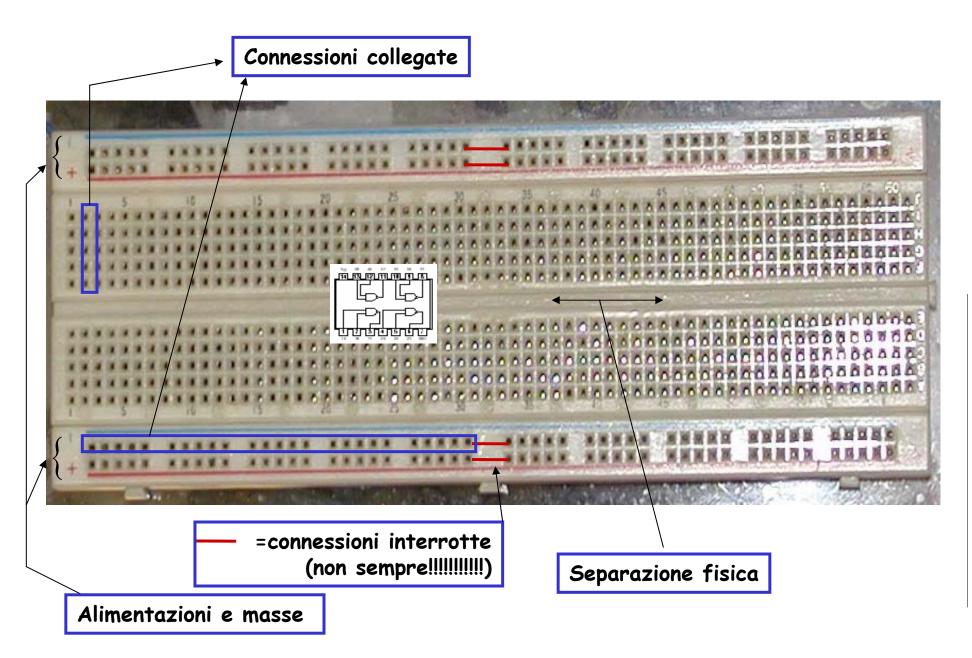

#### Come si usa la breadboard?

A.A. 2006-07 3° trimestre

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

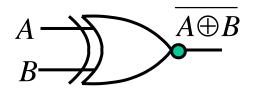

# Prime esperienze con le porte universali

- Verifica delle tavole della verità:

- Porte logiche fondamentali

- NAND a due ingressi

- NOR a due ingressi

- 2. Impiego delle porte NAND E NOR come:

- Inverter

- AND, OR con solo porte NAND, NOR

- Enable, Inhibit

- Mux, Demux

- EX-OR con quattro NAND

- EX-NOR con quattro NOR

- Comparatore digitale a un bit

- True/complement

- 3. Uso di integrati più complessi

- Complementazione di un numero binario a 4 bit con un 7486 (EXOR come True/Complement)

- Tavola della verità di una decodifica BCD-7segmenti

# Esperienza D-1

- a) Per effettuare operazioni logiche elementari

- b) Per la verifica del Teorema di De Morgan

- c) Per controllare il flusso di segnali digitali

### Preliminari alle singole prove:

- a) Comprende le prove

- Verifica delle tavole della verità di NAND (NOR) a due ingressi

- 2. Impiego di NAND(NOR) come inverter

- b) Comprende le prove

- 3. Uso di porte NAND (NOR) per realizzare AND(OR)

- 4. Uso di porte NAND (NOR) per realizzare una porta OR(AND)

- c) Uso di gates per operazioni di:

- 1. Enable, Inhibit

- a) .....è banale

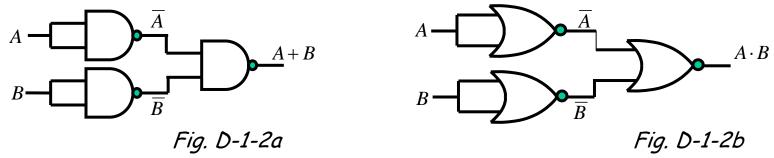

- b) Avevamo già visto che dal Teorema di De Morgan:

$$\overline{\overline{A} \cdot \overline{B}} = A + B$$

$\overline{\overline{A} + \overline{B}} = A \cdot B$

E' sufficiente realizzare il circuito corrispondente al primo membro e verificare che la sua tavola della verità sia uguale a quella del secondo membro.

Modificare i circuiti in modo che contengano solo porte NAND o solo porte NOR

A.A. 2006-07 3° trimestre

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

#### Materiale occorrente:

- 1. Laboratorio logico

- 2. IC: 7400, 7402,7404,7408,7432

- 3. Manuale IC

#### Come si procede:

- 1. Verificare le tabelle della verità di TUTTE le porte

- 2. Montare gli schemi di cui alle figure:

Usare il laboratorio logico che fornisce le alimentazioni per gli IC i segnali di ingresso (switch) ed i rivelatori di stato di uscita (led)

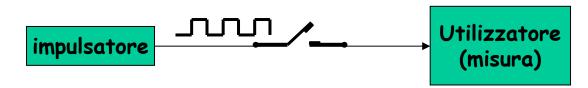

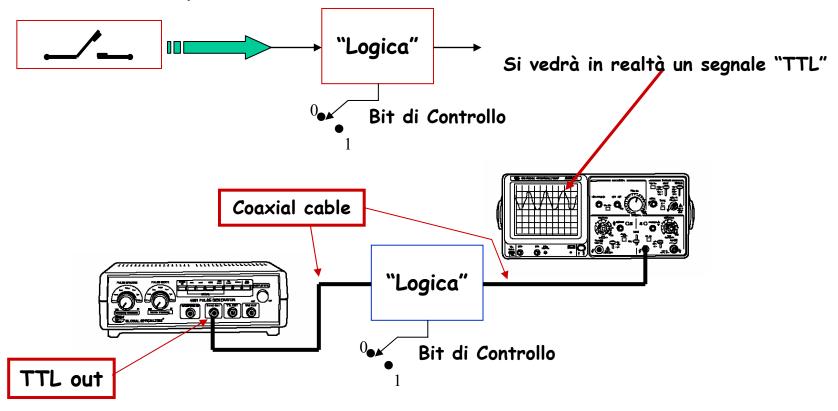

c) Operazioni di:Enable, Inhibit, True complement, Mux, Demux

Usare preliminarmente gli switch manuali ed i led dopo avere costruito il blocco "logica" sulla breadboard, poi l' FG ed il CRO (vedi il seguito)

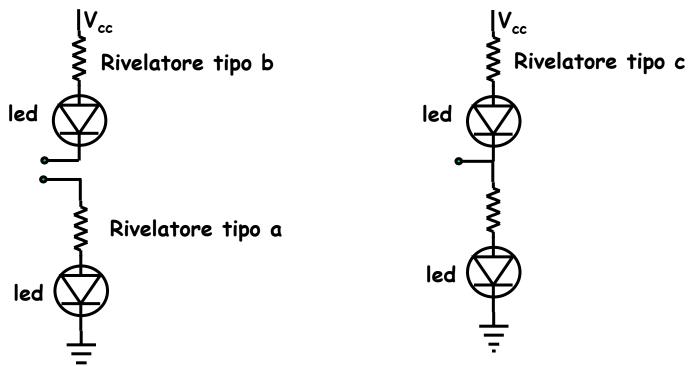

Cerchiamo di sostituire all' interruttore meccanico un meccanismo più sofisticato e pratico:

## Enable gate (strobe):

### Inhibit gate:

# Qualcosa di più su....Livelli e logiche

### Livelli:

1. LOGICI: V,F (T,F)

2. FISICI: H,L; (1,0)

## Logica:

1. <u>POSITIVA</u>: associazione tra il livello logico T e quello fisico H e quindi tra F e L

2. <u>NEGATIVA</u>: associazione tra il livello logico T e quello fisico L e quindi tra F e H

Esempio: il '7400 è una quadrupla NAND in logica positiva. Cosa sarebbe in logica negativa?

| В | Α | $\overline{A \cdot B}$ |

|---|---|------------------------|

| F | F | T                      |

| F | T | Т                      |

| Т | F | Т                      |

| Т | Т | F                      |

tavola della Verità "logica"

A.A. 2006-07 3° trimestre

| В | Α | $A \cdot B$ |                 | В | Α | X |

|---|---|-------------|-----------------|---|---|---|

| 0 | 0 | 1           |                 | 1 | 1 | 0 |

| 0 | 1 | 1           | Cambiamo logica | 1 | 0 | 0 |

| 1 | 0 | 1           |                 | 0 | 1 | 0 |

| 1 | 1 | 0           |                 | 0 | 0 | 1 |

Logica positiva

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

Una NOR

### Livelli attivi alti:

indica che un certo ingresso produce in uscita l'operazione specificata dal suo nome (Enable, Clear, Reset, Preset...... o segnala il verificarsi di una situazione indicata (es. A>B) quando quel terminale è alto.

#### 0.1

simboli usati nelle tabelle della verità facilmente associabili ai bit di un numero binario e sono da interpretarsi come "equivalenti" a T e F

## Blocchi logici:

### 1. Combinatori:

lo stato delle uscite in un certo istante, dipende solo dalla combinazione degli ingressi nello stesso istante ( a meno del tempo di propagazione del segnale)

## 2. Sequenziali:

lo stato dell'(e) uscita (e) in un certo istante, diopende(ono), oltre che dalla combinaziuone degli ingressi nello stesso istante, anche dai valori assunti in precedenza memorie

# N.B.

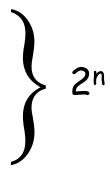

# Le funzioni booleane sono combinatorie

n bit: 2<sup>n</sup> combinazioni possibili funzioni booleane di n bit: colonne di m=2<sup>n</sup> bit si possono fare 2<sup>m</sup> colonne distinte

### FUNZIONI LOGICHE DI UNA VARIABILE:

| Α | F1 | F2 | F3 | F4 |

|---|----|----|----|----|

| 0 | 0  | 0  | 1  | 1  |

| 1 | 0  | 1  | 0  | 1  |

Es. TTL Texas '7487 True/complement/zero/one

## FUNZIONI LOGICHE DI DUE VARIABILI:

| В | Α | F0 | F1 | F2 | F3 | F4 | F5 | F6 | <b>F7</b> | F8 | F9 | F10 | F11 | F12 | F13 | F14 | F15 |

|---|---|----|----|----|----|----|----|----|-----------|----|----|-----|-----|-----|-----|-----|-----|

| 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0         | 1  | 1  | 1   | 1   | 1   | 1   | 1   | 1   |

| 0 | 1 | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1         | 0  | 0  | 0   | 0   | 1   | 1   | 1   | 1   |

| 1 | 0 | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1         | 0  | 0  | 1   | 1   | 0   | 0   | 1   | 1   |

| 1 | 1 | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1         | 0  | 1  | 0   | 1   | 0   | 1   | 0   | 1   |

A.A. 2006-07 3° trimestre

R O R R Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/ N A N D 7

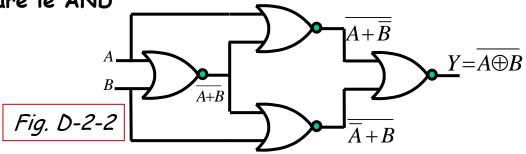

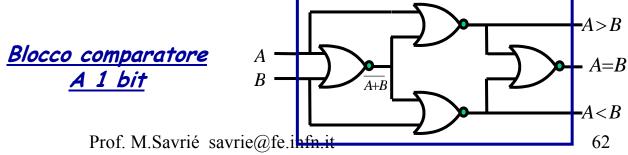

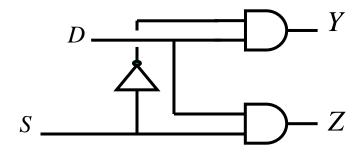

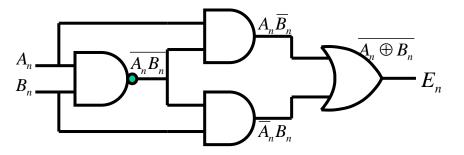

# Esperienza D-2

### Comprende le prove:

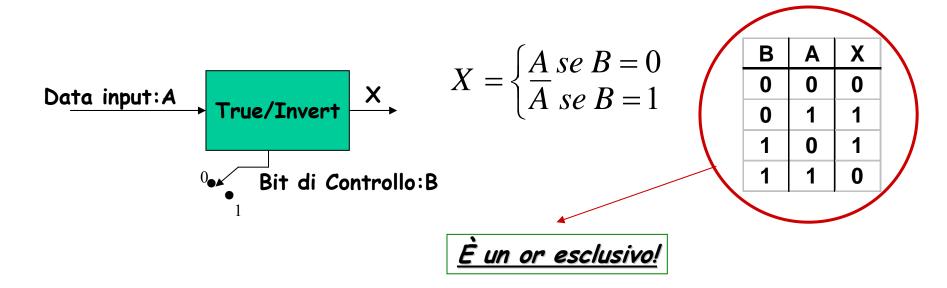

- Realizzazione di un True/Complement (True/Invert)

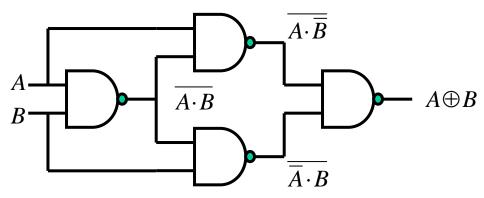

- Realizzazione di un XOR(XNOR) con sole NAND e NOR

- Funzione di eguaglianza

- Comparatore digitale a 1 bit

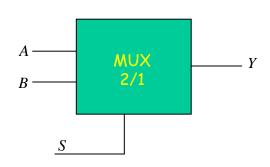

- Mux

- Demux

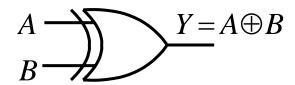

| В | A | $A \oplus B$ |

|---|---|--------------|

| 0 | 0 | 0            |

| 0 | 1 | 1            |

| 1 | 0 | 1            |

| 1 | 1 | 0            |

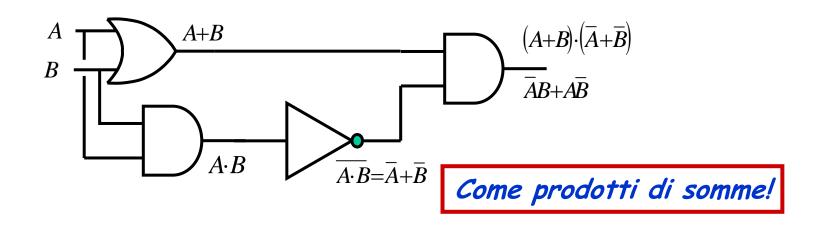

E' uguale alla OR tranne che vale zero se A=B=1.Quindi:

è vera se : è vera

$$(A + B)$$

ed è falsa  $A \cdot B$

$$XOR(A,B) = (A+B) \cdot \overline{AB}$$

# Come somme di prodotti

#### Dalla tavola della verità:

| В | Α | $A \oplus B$ |

|---|---|--------------|

| 0 | 0 | 0            |

| 0 | 1 | 1            |

| 1 | 0 | 1            |

| 1 | 1 | 0            |

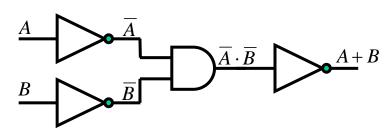

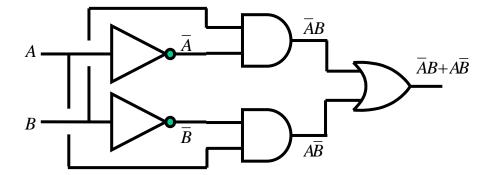

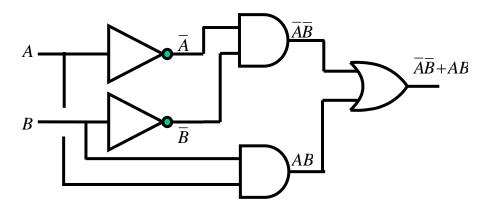

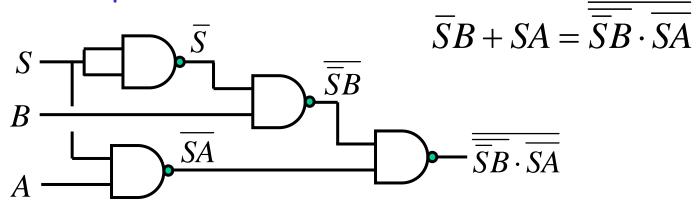

# Ma sono 5 porte! E si può migliorare....con: De Morgan

$$\overline{A}B + A\overline{B} = \overline{\overline{A}B \cdot A\overline{B}}$$

**Infatti:**

$$\overline{A \cdot B} \cdot B = (\overline{A} + \overline{B}) \cdot B = B \cdot \overline{A} + \overline{B} \cdot B = \overline{A} \cdot B$$

$$\mathbf{Ma} : \qquad \overline{\overline{A}B} = \overline{B \cdot \left( \overline{A} + \overline{B} \right)} = \overline{B} + \left( \overline{\overline{A} + \overline{B}} \right) = \overline{B} + AB = \overline{B \cdot \overline{AB}}$$

Da cui:

$$\overline{A}B + A\overline{B} = \overline{AB} \cdot B \cdot A \cdot \overline{AB}$$

A.A. 2006-07 3° trimestre

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

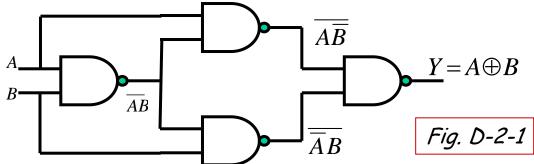

### Oppure per la XNOR:

| В | Α | $\overline{A \oplus B}$ |

|---|---|-------------------------|

| 0 | 0 | 1                       |

| 0 | 1 | 0                       |

| 1 | 0 | 0                       |

| 1 | 1 | 1                       |

# Ma sono 5 porte! E si può migliorare.....con: De Morgan

La funzione vale 1 solo se A=B (funzione di eguagianza e complemento della XOR). Per De Morgan il complemento si ottiene: <u>scambiando le AND con le OR e complementando le variabili di ingresso.</u> In questo caso però l' ultima operazione di complementazione non modifica la tavola della verità:

$XNOR(A,B) = XNOR(\overline{A}, \overline{B})$

per cui è sufficiente scambiare le AND con le OR:

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

#### Realizzazione Pratica:

1. usare un I.C. 7400 (quadrupla NAND a due ingressi) per realizzare lo schema (fig. D-2-1) e ricavarne la tavola della verità;

| В | A | $A \oplus B$ |

|---|---|--------------|

| 0 | 0 | 0            |

| 0 | 1 | 1            |

| 1 | 0 | 1            |

| 1 | 1 | 0            |

Se si usa una delle variabili (es. B) come bit di controllo:

$$B = 0 \Rightarrow Out = A$$

$B = 1 \Rightarrow Out = \overline{A}$

True/complement

2. usare un I.C. 7402 (quadrupla NOR a due ingressi) per realizzare lo schema (fig. D-2-2) e ricavarne la tavola della verità;

| В | Α | $\overline{A \oplus B}$ |

|---|---|-------------------------|

| 0 | 0 | 1                       |

| 0 | 1 | 0                       |

| 1 | 0 | 0                       |

| 1 | 1 | 1                       |

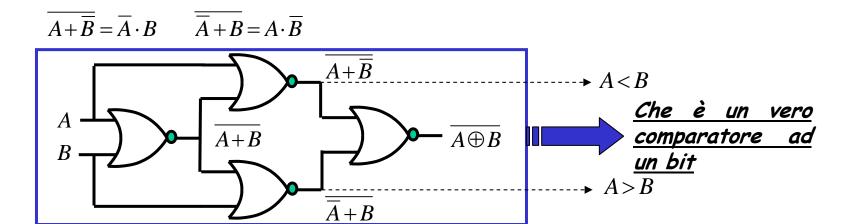

- · E' vera quando sono diversi gli ingressi

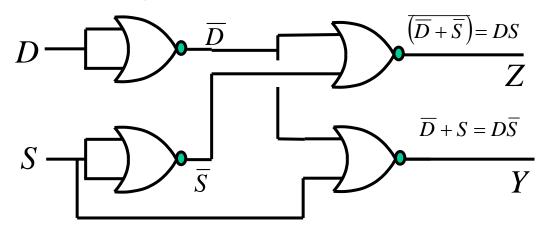

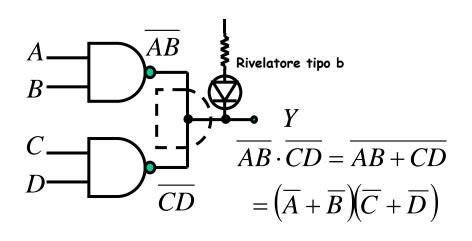

- · la porta di uscita (NOR nella fig.D-2-2) è falsa quando o l'uno o l'altro dei due ingressi sono veri-> i due ingressi devono rappresentare A>B e A<B:

A.A. 2006-07 3° trimestre

http://www.fe.infn.it/~savrie/

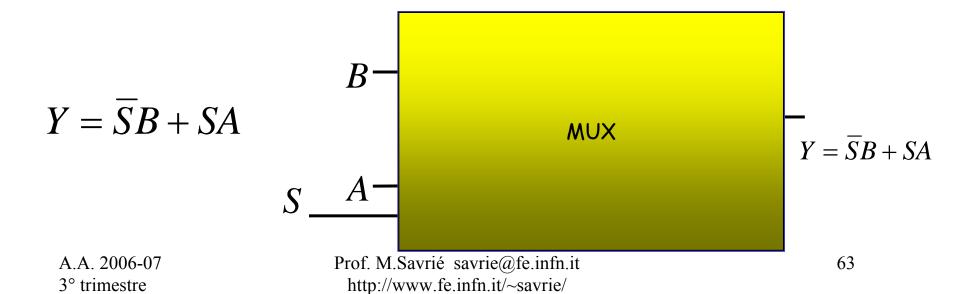

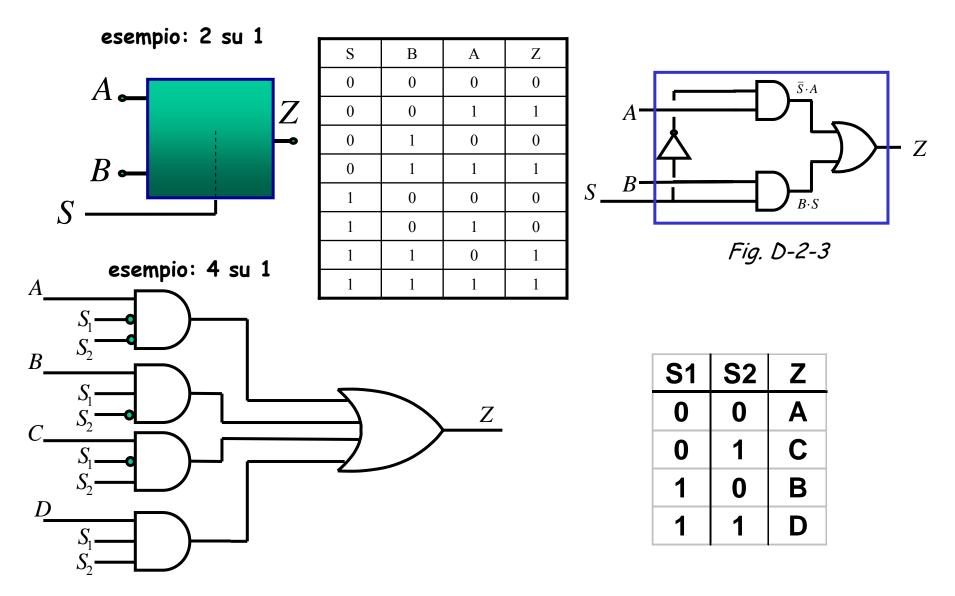

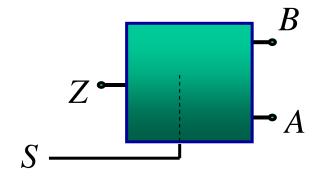

# Multiplexers e .....

| S | Α | В | Υ |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

| S | Α | В | Y |

|---|---|---|---|

| 0 | х | х | В |

| 1 | Х | Х | Α |

COME PREVEDIBILE ABBIAMO UNA SOLA FUNZIONE LOGICA:

$$Y = \overline{A}B\overline{S} + AB\overline{S} + A\overline{B}S + ABS$$

## Multiplexer (italiano: selettore):

A.A. 2006-07 3° trimestre

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

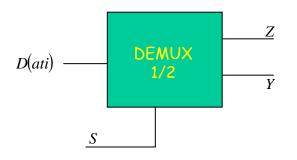

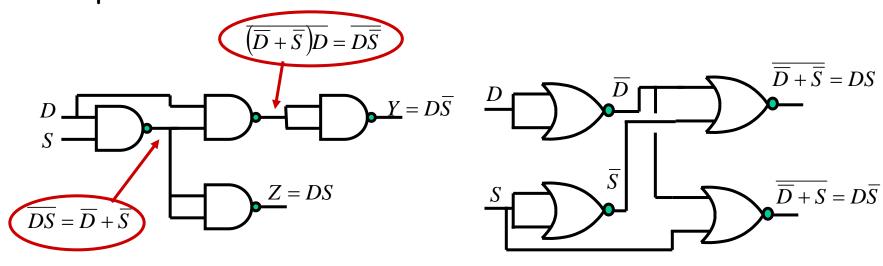

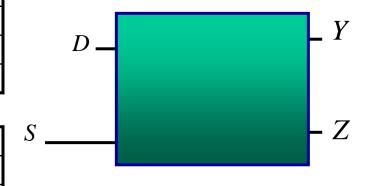

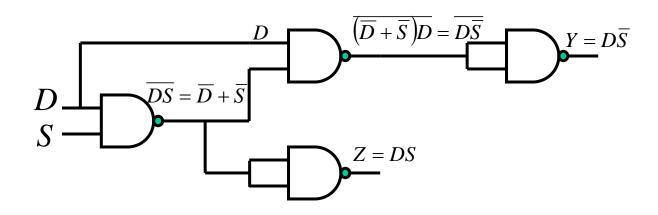

# ......<u>Demultiplexers</u>

| S | D | Z | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 |

| S | D | Z | Y |

|---|---|---|---|

| 0 | х | 0 | D |

| 1 | X | D | 0 |

COME PREVEDIBILE ABBIAMO DUE FUNZIONI LOGICHE:

$$Z = \underline{S}D$$

$$Y = \overline{S}D$$

### Con le porte universali:

A.A. 2006-07 3° trimestre

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

## Demultiplexer:

esempio: 1 su 2

| S | D | y | Z |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 |

| S | D | y | Z |

|---|---|---|---|

| 0 | X | D | 0 |

| 1 | X | 0 | D |

Fig. D-2-4

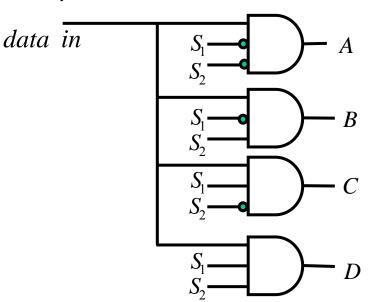

esempio: 1 su 4

| <b>S</b> 1 | S2 OUT |   |

|------------|--------|---|

| 0          | 0      | Α |

| 0          | 1      | В |

| 1          | 0      | С |

| 1          | 1      | D |

A.A. 2006-07 3° trimestre

Prof. M.Savrié savrie@fe.infn.it http://www.fe.infn.it/~savrie/

## Demultiplexer con sole porte NAND:

### Demultiplexer con sole porte NOR:

### Multiplexer con sole porte NAND:

Multiplexer con sole porte NOR: più di 4->non è utile adesso

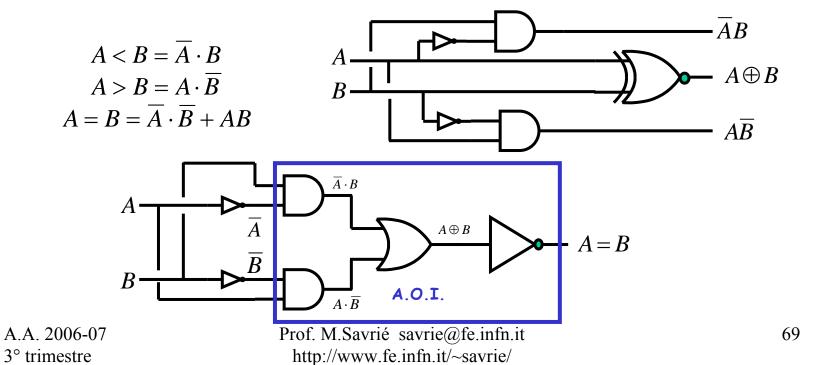

# Comparatore

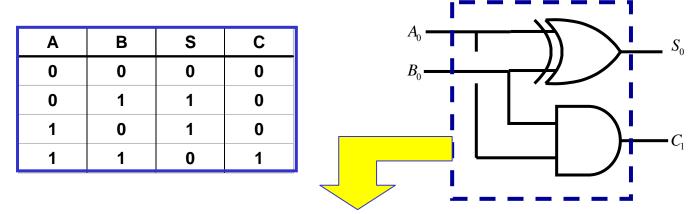

### Partiamo dal caso più semplice a 1 bit:

| Α | В | A <b< th=""><th>A=B</th><th>A&gt;B</th></b<> | A=B | A>B |

|---|---|----------------------------------------------|-----|-----|

| 0 | 0 | 0                                            | 1   | 0   |

| 0 | 1 | 1                                            | 0   | 0   |

| 1 | 0 | 0                                            | 0   | 1   |

| 1 | 1 | 0                                            | 1   | 0   |

COME PREVEDIBILE ABBIAMO TRE FUNZIONI LOGICHE:

Avevamo già visto come fare un EXOR con 4 porte NAND

Ma è anche più immediato se si relaizza mediante NOR infatti per De Morgan:

.....lo riprenderemo più avanti!

#### Condotta Pratica:

- 1. Assemblare il circuito MUX 2 su 1 (fig D-2-3)

- · Realizzare il MUX con sole NAND

- 2. Asseblare il circuito Demux 1 su 2

- · Realizzarlo anche con sole NAND o NOR

- 3. Provare ciascuno dei circuiti con gli interruttori manuali

- 4. Provare ciascun circuito con generatore di Funzioni (F.G.) e oscilloscopio (C.R.O.)

- 5. provare un comparatore ad 1 bit

- 6. Provare anche 74153 (dual quad-in MUX)

- 7. Provare anche 74154 (4in-16 out)

- 8. Provare un 7485 (comparatore a 4 bit)

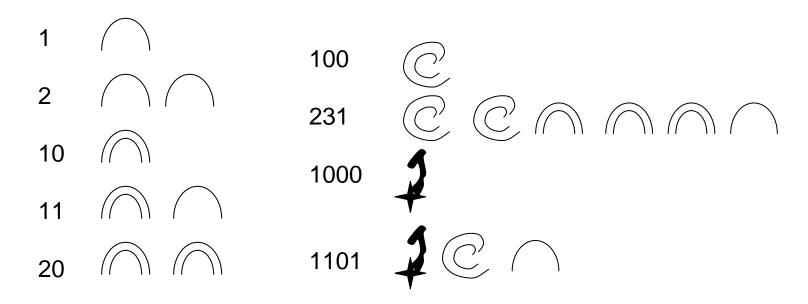

## Sistemi di Numerazione

- Numero

- concetto non primitivo

- serve per "quantificare" la realtà

- Sistema di numerazione:

- insieme finito di simboli

- simboli organizzati in sequenze secondo "regole"

Il sistema più antico è (forse) quello egizio ed ha circa 5000 anni. E' di tipo decimale con simboli ripetuti per i multipli di una stessa quantità.

# • I Sumeri avevano l'unità numerica fondamentale che corrisponde al nostro 60

nostra misurazione degli angoli?

# Non hanno lo zero ed i simboli sono posizionali

- lo zero introdotto forse nella civiltà indiana e poi arriva in Europa portato dagli Arabi

- I simboli da noi usati oggi (indo-Arabi) risalgono al X secolo

- I numeri frazionari arrivano solo nel XVI secolo

- Il punto decimale viene introdotto verso la metà del XVII secolo

Basi: numero di simboli usati nella numerazione

Posizionale: sistema in cui il valore di associato ad ogni simbolo dipende dalla sua posizione nella "stringa"

Peso: il fattore per cui il simbolo (numero) deve esse moltiplicato per potere essere confrontato con gli altri simboli (numeri): potenza ad esponente variabile della base del sistema di numerazione

# Sitema decimale:

- è in base 10

- 10 simboli: 0-9

- è posizionale

**Esempio:** 4518,23

Che significa:

4000+500+10+8+0,2+0,03

# Sitema binario:

- è in base 2

- 2 simboli: 0,1

- è posizionale

**Esempio: 1001,01**

1 0 0 1, 0 1 2<sup>3</sup> 2<sup>2</sup> 2<sup>1</sup> 2<sup>0</sup>, 2<sup>-1</sup> 2<sup>-2</sup>

Che significa:

8+0+0+1+0+0.25

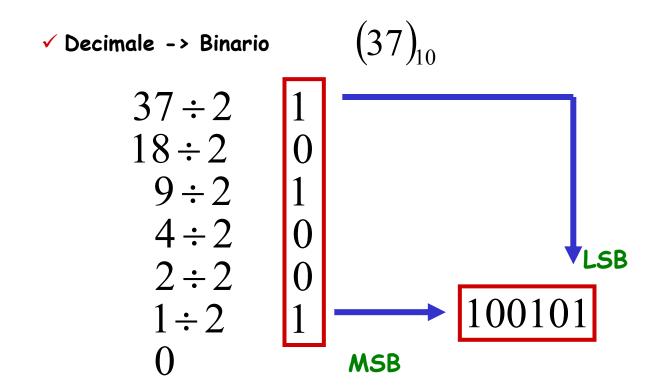

# Come si passa da un sistema all' altro?

$$(1100101)_2 =$$

$$1 \cdot 2^6 + 1 \cdot 2^5 + 0 \cdot 2^4 + 0 \cdot 2^3 + 1 \cdot 2^2 + 0 \cdot 2^1 + 1 \cdot 2^0 = (101)_{10}$$

# Sitema ottale:

- è in base 8

- 8 simboli: 0-7

- è posizionale

**Esempio:** (514,23)<sub>8</sub>

5 1 4, 2 3 8<sup>2</sup> 8<sup>1</sup> 8<sup>0</sup>, 8<sup>-1</sup> 8<sup>-2</sup>

Esempio: (456)<sub>8</sub>

$1_{1}0_{1}0_{1}1_{1}0_{1}1_{1}1_{1}0_{1}$

# Sitema esadecimale:

- è in base 16

- 16 simboli: 0-9,A,B,C,D,E,F

- è posizionale

Esempio: (3AFF9)<sub>16</sub>

Esempio:(B7F)<sub>16</sub>

| 1<sub>1</sub>0<sub>1</sub>1<sub>1</sub>1|0<sub>1</sub>1<sub>1</sub>1<sub>1</sub>1|1<sub>1</sub>1<sub>1</sub>1

# Esempio paratico di progetto (parziale)

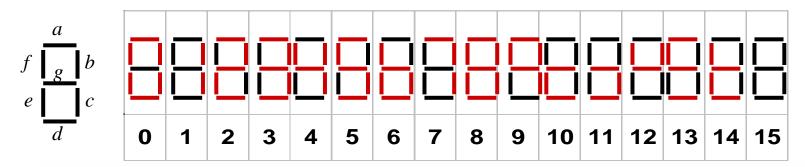

# Convertitore BCD-7 segmenti

**BCD**: binary coded decimal

7 segmenti: è un tipo di display

$$\begin{array}{c|c}

a \\

f & g \\

\hline

e & c

\end{array}$$

# Come si procede:

- 1. Dobbiamo rappresentare i numeri da 0 a 9: di quanti bit abbiamo bisogno?

- 2. Quale (i) è (sono) la (le ) funzione (i) logica?

- 3. Come si costruisce (ono)?

'46A, '47A, 'LS47 FUNCTION TABLE (T1)

| DECIMAL  |          |       | INP | JTS |   |   | BI/RBO† |     |     | 0   | UTPUI | s   |     |     | NOTE |

|----------|----------|-------|-----|-----|---|---|---------|-----|-----|-----|-------|-----|-----|-----|------|

| FUNCTION | LT       | RBI   | D   | С   | В | Α |         | а   | ь   | c   | d     | е   | f   | g   |      |

| 0        | н        | н     | L   | L   | L | L | н       | ON  | ON  | ON  | ON    | ON  | ON  | OFF |      |

| 1 1      | н        | ×     | L   | L   | L | н | н       | OFF | ON  | ON  | OFF   | OFF | OFF | OFF |      |

| 2        | н        | ×     | L   | L   | н | L | н       | ON  | ON  | OFF | ON    | ON  | OFF | ON  |      |

| 3        | _ н      | ×     | L   | L   | н | н | н       | ON  | ON  | ON  | ON    | OFF | OFF | ON  |      |

| 4        | Н        | ×     | L   | н   | L | L | н       | OFF | ON  | ON  | OFF   | OFF | ON  | ON  |      |

| ] 5      | н        | ×     | L   | н   | L | н | н       | ON  | OFF | ON  | ON    | OFF | ON  | ON  |      |

| 6        | ( н      | ( × ( | L   | н   | н | Ĺ | } **    | OFF | OFF | ON  | ON    | ON  | ON  | ON  |      |

| 7        | н        | ×     | L_  | н   | н | н | н       | ON  | ON  | ON  | OFF   | OFF | OFF | OFF |      |

| 8        | н        | ×     | H   | L   | L | L | н       | ON  | ON  | ON  | ON    | ON  | ON  | ON  | 1    |

| 9        | ίн       | ×     | н   | L   | L | н | н       | ON  | ON  | ON  | OFF   | OFF | ON  | ON  |      |

| 10       | н        | ×     | н   | L   | н | L | н       | OFF | OFF | OFF | ON    | ON  | OFF | ON  |      |

| 11       | н        | x     | н   | L   | н | н | н       | OFF | OFF | ON  | ON    | OFF | OFF | ON  |      |

| 12       | Н        | X     | н   | н   | L | L | н       | OFF | ON  | OFF | OFF   | OFF | ON  | ON  |      |

| 13       | н        | ×     | н   | н   | L | н | н       | ON  | OFF | OFF | ON.   | OFF | ON  | ON  | }    |

| 14       | н        | ×     | н   | н   | н | L | н       | OFF | OFF | OFF | ON    | ON  | ON  | ON  |      |

| 15       | н        | ×     | .н  | н   | н | н | н       | OFF | OFF | OFF | OFF   | OFF | OFF | OFF |      |

| 81       | ×        | ×     | ×   | ×   | × | × | L       | OFF | OFF | OFF | OFF   | OFF | OFF | OFF | 2    |

| RBI      | н        | L     | L   | L   | L | L | L       | OFF | OFF | OFF | OFF   | OFF | OFF | OFF | 3    |

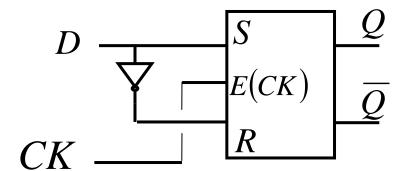

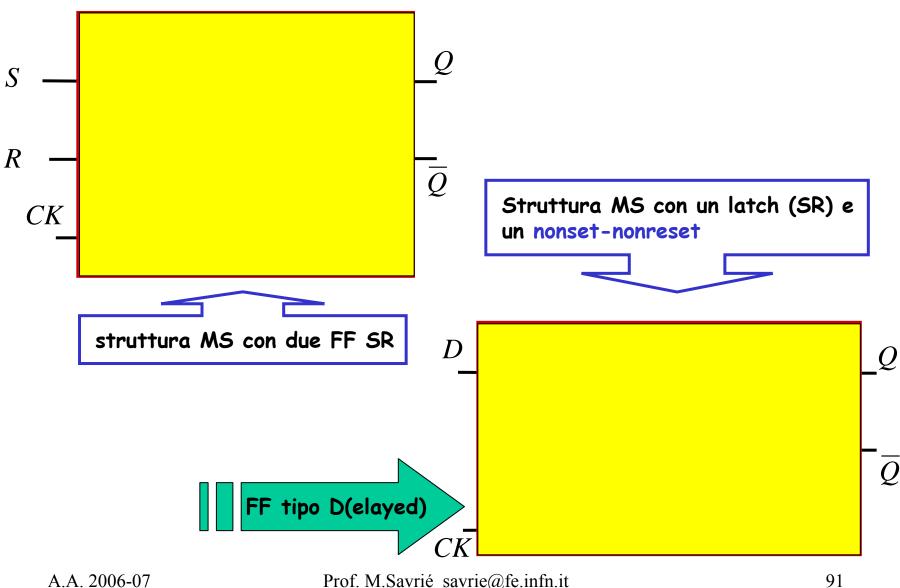

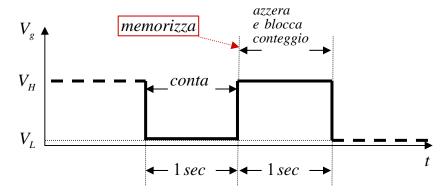

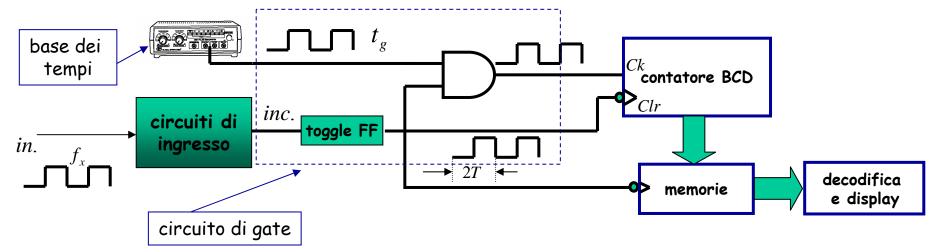

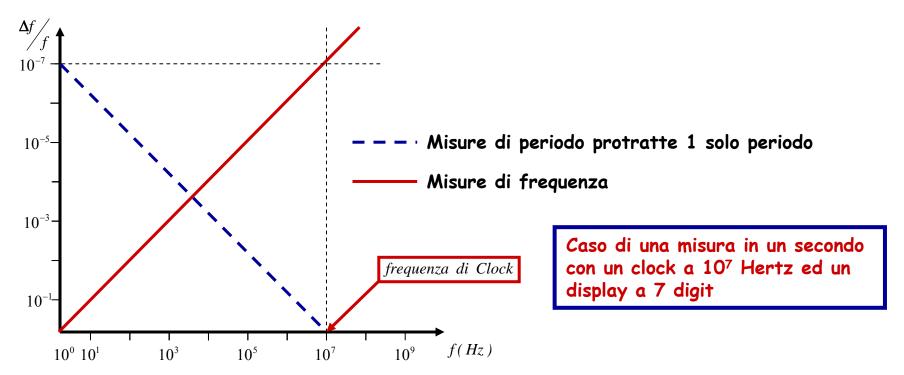

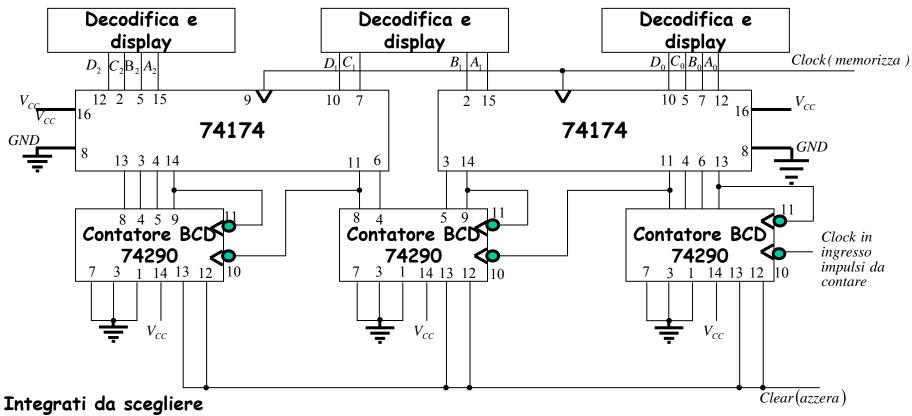

| LT       | <u> </u> | ×     | ×   | ×   | х | x | н       | ON  | ON  | ON  | ON    | ON  | ON  | ON  | 4    |